# CHARGE INJECTION TRANSISTORS AND LOGIC CIRCUITS

# Serge Luryi

AT&T Bell Laboratories, Murray Hill, NJ 07974, USA

(Received 27 September, 1990)

The charge injection transistor or CHINT is a semiconductor device based on real-space transfer of hot electrons between two conducting layers, separated by a potential barrier. Recently, significant progress has been achieved at Bell Laboratories in the implementation of CHINT devices. Using InGaAs/InAlAs heterostructure materials and novel epitaxial contacts, nearly ideal characteristics were obtained, e.g. an NDR with a peak-to-valley ratio approaching  $10^4$  at room temperature and a transconductance  $g_m > 20\,\mathrm{S/mm}$ . The nature of hot-electron injection in CHINT allows the implementation of novel circuit elements. In particular, we have proposed and demonstrated a multiterminal single-device structure that works as a functional element with three symmetric logic inputs  $X_1, X_2, X_3$  and one output equal to  $(X_1 \cap X_2 \cap X_3) \cup (\overline{X}_1 \cap \overline{X}_2 \cap \overline{X}_3)$ . This device, called the NORAND, can perform both as a  $NOR(X_1, X_2)$  and as an  $AND(X_1, X_2)$  element, reprogrammable electrically by changing the  $X_3$  input. The NORAND element permits the implementation of circuits in which the function of a particular logic element is not fixed by the layout but is reprogrammable in the course of the circuit operation.

### 1. INTRODUCTION

The charge-injection transistor (CHINT) or negative resistance field-effect transistor (NERFET) are two three-terminal modes of operation of а heterostructure device [1-3] based on the real-space transfer of hot electrons. The concept of realspace-transfer (RST) [4] describes the process in which electrons in a narrow semiconductor layer, accelerated by an electric field parallel to the layer, acquire high average energy (become "hot") and then spill over an energy barrier into the adjacent layers. Even though only a small fraction of electrons, those in the high-energy tails of the hotcarrier distribution function, can participate in this process, those tails are replenished at a fast rate corresponding to the energy relaxation time, mainly owing to electron-electron collisions. Multiple collisions result in a Gaussian distribution of carrier velocities, which can be interpreted as a Maxwellian ensemble with an effective electron temperature  $T_e$ . The injection process is then analogous to the usual thermionic emission, and for high  $T_e$  it can be very efficient.

The original idea of employing the RST in devices was to induce a negative differential resistance (NDR) in multilayered structures [4-5], an effect discovered experimentally [6] and studied in

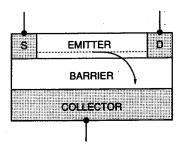

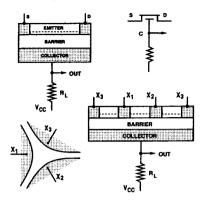

Figure 1: Schematic diagram of a charge injection transistor. The arrow shows the direction of electron flow.

great detail [7]. Transistor applications of the RST began with the proposal [1] of a three-terminal structure where hot-electron injection occurs between two conducting layers isolated by a potential barrier and contacted separately. This structure is illustrated in Fig. 1. One of the two layers ("emitter") has source and drain contacts and plays the role of a hot-electron cathode. The other layer ("collector") is separated by a potential barrier. When the emitter electrons are heated by the source-drain field most of them do not reach the drain but are injected over the barrier into the collector layer; a strong negative differential resistance (NDR) develops in the drain circuit. The transistor action results from an efficient control of the electron temperature  $T_e$  and hence the injection current  $I_C$  by the input voltage  $V_D$ .

A number of functional applications have been unique contemplated [8-11], based on the devices. characteristics of three-terminal RST Recently, the scope of such applications was expanded by the invention [12] of a new structure, called multiterminal device NORAND. The principle of NORAND embodies the basic symmetry inherent in the charge injection by RST: direction of the collector current is the same irrespective of the polarity of the heating voltage, i.e. it does not matter which of the surface electrodes plays the role of the source and which of the drain. The operation of NORAND has been demonstrated experimentally and will be discussed in this paper (Sect. 4). This discussion will be preceded by a review of the recent progress in the implementation of charge injection transistors.

injection transistors Charge extensively studied, both experimentally [13-20] and theoretically [21-26]. The early investigations were based on GaAs/AlGaAs heterostructures. This work has been reviewed in Refs. [11] and [26]. More recently, there have been reports of the implementation of RST transistors in strained-layer InGaAs/AlGaAs heterostructures grown on GaAs substrates [15-17]. In most of these structures, the RST is likely to be accompanied by a momentumspace transfer, which limits the intrinsic performance of CHINT/NERFET devices. Monte Carlo simulations [25] have shown that formation of Gunn domains lowers the NDR peak-to-valley ratio and limits the ultimate device speed. It is of considerable interest, therefore, to implement these devices in materials where the momentum-space transfer would be absent or negligible relative to the RST. Working in this direction, several groups [18-19] have recently realized three-terminal RST devices, based on the injection of hot holes across a potential discontinuity in the valence band of GaAs/AlGaAs and GeSi/Si heterojunctions.

Another attractive material combination is the In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As system lattice-matched to InP. Advantages of this system for RST transistors stem from the low effective electron mass  $m = 0.042 m_0$  in the  $\Gamma$  valley of InGaAs, the high conduction-band discontinuity ( $\Delta E_C \approx 0.5 \,\text{eV}$ ), and the still higher satellite-valley separation  $(\Delta E_{\Pi} \approx 0.55 \,\text{eV})$  [27]. One can expect that if the effective barrier height for charge injection (which is less than  $\Delta E_C$ ) is lower than  $\Delta E_{\Gamma L}$ , then the RST should have a lower threshold than the Gunn effect. The relatively large  $\Delta E_C$  (compared to  $GaAs/Al_rGa_{1-r}As$  for x < 0.4) allows one to expect a lower leakage current of "cold" electrons and, hence, an improved performance at room temperature. The lower effective mass favors the efficiency of electron heating in an electric field. Although these advantages were apparent a long time ago [2], they had not been exploited until recently because of the difficulties in implementing non-shorting ohmic contacts. Previous attempts at implementation of CHINT/NERFET in this system were not successful: the usual Au-Ge alloved contacts to the channel either showed non-ohmic behavior [9] or, if alloyed at an elevated temperature, penetrated too deep, resulting in an electrical short to the collector. This essential problem was solved recently [13] by using an epitaxially-grown cap layer, heavily doped with tin, which is subsequently patterned lithographically to form the source and drain  $n^+$  contacts.

# 2. DEVICE STRUCTURE

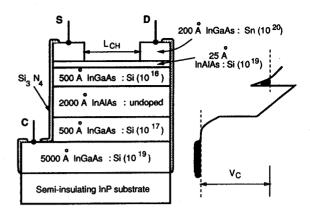

The structure described below was reported in Ref. [14]; it represents an improvement in several respects over the earlier study [13]. Figure 2 shows a cross section of the device obtained after several wet chemical etching and ion milling steps. The heterostructure has been grown by molecular beam epitaxy at 550C on a semi-insulating iron-doped InP (100) substrate. It consists of the following layer sequence: a 5000 A-thick n+ In<sub>0.53</sub>Ga<sub>0.47</sub>As collector layer followed by a 500 A-thick lightly doped n-In<sub>0.53</sub>Ga<sub>0.47</sub>As setback layer, a 2000 Athick undoped In<sub>0.52</sub>Al<sub>0.48</sub>As barrier layer, and a lightly doped 500 A-thick In<sub>0.53</sub>Ga<sub>0.47</sub>As emitter layer, followed by a 25 A-thick n+In<sub>0.52</sub>Al<sub>0.48</sub>As etch-stop layer, and an ultra-heavily doped (Sn) 200 A-thick In<sub>0.53</sub>Ga<sub>0.47</sub>As cap layer.

The active area of the device represents a strip of the emitter layer whose dimension along the line connecting the source and drain is 9.5 µm and the width W varies from 25 µm to 75 µm. All patterns were defined by the standard optical contact lithography, including the critical definition of a trench separating the source and drain areas. This trench, 200 A-deep, defines the emitter channel. It is obtained by a highly selective wet chemical etching of In<sub>0.53</sub>Ga<sub>0.47</sub>As, which stops reliably at a 25 A-thick In<sub>0.52</sub> Al<sub>0.48</sub> As layer introduced specially for that purpose. For different devices, the trench length  $L_{ch}$  varied from 0.6  $\mu$ m to 5  $\mu$ m. After the etching, the exposed portion of the channel is entirely depleted by the surface potential, but with a positive voltage applied to the collector, a twodimensional electron gas is induced in the channel, as illustrated in Fig. 2.

Contacts to the channel were ohmic down to liquid He temperatures. We found no degradation of the contacts from the introduction of the 25 Å-thick InAlAs etch-stop layer.

An important element in the structure is the lightly-doped setback layer between the barrier and the collector. Its purpose is to reduce the possibility of an unintentional doping of the barrier during growth by an out-diffusion of donors from the collector. Compared to structures without the setback layer [13] the dielectric strength of the barrier is substantially enhanced.

#### 3. STATIC CHARACTERISTICS

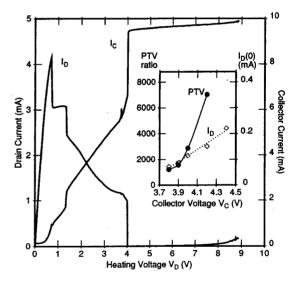

Figure 3 shows the current-voltage characteristics of a  $25\,\mu\text{m}$ -wide  $1\,\mu\text{m}$ -long device at  $T=300\,\text{K}$ . The striking feature is a NDR in the drain characteristic with a peak-to valley (PTV) ratio typically exceeding 1000 at room temperature. In contrast to most of the previous studies of the device, this strong NDR is obtained in the presence of a low leakage current due to "cold electrons". We see that the NERFET switches almost the entire source current from the drain branch of the biasing circuit to the collector branch. The resulting collector current  $I_{\text{C}}$  is more than twice larger than the peak value of  $I_{\text{D}}$ .

As the inset to Fig. 3 shows, both the leakage current and the PTV ratio are increasing functions of the collector voltage. At  $V_{\rm C}=4.4\,\rm V$ , the observed PTV exceeds 7000. Our measure of the leakage is the value of  $I_{\rm D}$  at  $V_{\rm D}=0$ ; in a perfectly symmetric device it equals half the value of  $I_{\rm C}$  at the same bias. Within the limit of  $V_{\rm C}$  imposed by a dielectric breakdown of the  $I_{\rm N}$ 0.52 $AI_{\rm N}$ 48 layer,

Figure 2: Cross-section of the device structure and the energy-band diagram under an applied collector bias [14]. The trench in the heavily Sn-doped cap layer defines the emitter channel.

Figure 3: Room temperature characteristics [14] of a CHINT/NERFET device with  $W=25\,\mu\mathrm{m}$  and  $L_{\mathrm{ch}}=1\,\mu\mathrm{m}$ . The drain current  $(I_{\mathrm{D}})$  and collector current  $(I_{\mathrm{C}})$  are plotted versus the heating drain voltage  $V_{\mathrm{D}}$  at a fixed collector bias  $V_{\mathrm{C}}=3.9\,\mathrm{V}$ . Insert shows the collector-bias dependence of the peak-to-valley ratio and the leakage current, defined as the magnitude of  $I_{\mathrm{D}}$  at  $V_{\mathrm{D}}=0$ .

we observed no tendency toward saturation in either PTV or  $I_D(0)$ . The dielectric strength of the barrier and its abruptness at the collector side is evidenced by the low leakage at  $V_D=0$  and also by the broad valley in  $I_D$  at high drain biases. As seen

in Fig. 3, this valley persists up to  $V_D - V_C \approx 5 \text{ V}$ , until it is overwhelmed by an injection of "cold electrons" from the collector.

The variation of  $V_{\rm C}$  affects not only the PTV ratio but also the critical voltage,  $V_{\rm NDR}$ , for the onset of NDR. At high collector voltages the  $V_{\rm NDR}$  shifts to lower values. It is likely that this shift is due to the increased importance of the tunneling process in the RST [21]. At high  $V_{\rm C}$ , the charge injection occurs via "thermally" assisted tunneling. This is equivalent to an effective lowering of the barrier height; a given RST current is therefore realized at a lower electron temperature, and hence at a lower  $V_{\rm D}$ .

Because the electron temperature in the channel is controlled by the drain field that at a fixed  $V_{\rm D}$  increases with decreasing  $L_{\rm ch}$ , the  $V_{\rm NDR}$  shifts to lower values for shorter channel lengths [14]. In devices with  $L_{\rm ch}=0.6\,\mu{\rm m}$ , the onset of the NDR is observed at drain voltages as low as 0.34 V. Note that this  $V_{\rm NDR}$  includes the voltage drop in the contacts but still is appreciably lower than the barrier height  $\Delta E_{C}/e\approx0.5\,{\rm V}$ . This provides an evidence that the RST proceeds from the tails of a "thermalized" hot-electron distribution function rather than by a single-event scattering of ballistically accelerated electrons.

A fundamentally interesting question is: what limits the real space transfer in CHINT/NERFET structures? Figure 3 clearly indicates that if we were able to apply higher collector bias without a breakdown of the barrier the PTV ratio would increase even further. At the same time, for a given  $V_C$  both the valley and the injection currents reach relatively flat plateau values as a function of the heating voltage. This indicates a breakdown of the electron temperature approximation. Indeed, for a given Te the RST process depletes the channel exponentially with the distance toward the drain without a limit [8]. Since with increasing VD the high-field region expands like it does in a fieldeffect transistor (as the pinch-off point moves toward the source), theories based on the  $T_e$ approximation [21] predict an exponential decrease of  $I_D$  with increasing heating voltage.

Monte Carlo studies [24,25] have shown that in GaAs/AlGaAs devices the RST process is limited by a momentum-space transfer of hot electrons into the satellite valleys, that cuts off the heating of channel electrons. It is unlikely, however, that momentum-space transfer effects could play a significant role when the satellite-valley separation is much higher than the effective barrier height. We

believe that such is the situation in our present devices, at least at high  $V_{\rm C}$ . In the absence of momentum-space transfer, the RST process can be self-limited, when the electron concentration n in the channel drops below a certain critical value  $n_{\rm CT}$  that itself is a function of the barrier height and therefore of  $V_{\rm C}$ . As the data in Fig. 3 indicate, the drain current at the valley is below 1 mA/cm. This corresponds to  $n \le 10^9$  cm<sup>-2</sup>. At such low carrier concentrations, the assumption of a Maxwellian ensemble, characterized by a single  $T_{\rm e}$ , can be expected to break down [26].

Indeed, such an ensemble is established when the electron-electron scattering time is shorter than the relaxation time associated with the lattice. At low electron concentrations, the high-energy portion of the energy distribution that is constantly depleted by the RST, is no longer efficiently refilled and can be strongly depressed compared to a Maxwellian curve. Although the total distortion of the distribution function is "integrally" weak, because it affects only the tails of the distribution containing a small fraction of electrons, in those very tails the distortion can be quite strong [28]. This means that one can expect a self limitation of the RST process with the channel concentration never dropping below a critical level - determined, for a given collector barrier height, by the concentration dependence of the electron-electron interaction.

The importance of interelectronic interactions and cooperative effects in CHINT cannot be overemphasized, although at present our description of these processes is at best qualitative. Such effects are likely to be important for a quantitative understanding of the phenomenon of ultra-high transconductance, discussed below.

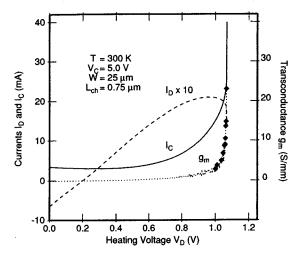

The transconductance, gm is an important figure of merit for any transistor. For the CHINT, it is defined as the slope of the  $I_C(V_D)$  characteristic per unit width W of the emitter channel:  $g_{\rm m} \equiv W^{-1} \partial I_{\rm C} / \partial V_{\rm D}$  at a constant  $V_{\rm C}$ . GaAs/AlGaAs CHINT the highest reported [11] transconductance was  $g_m \approx 1,000 \,\text{mS/mm}$ . The transconductance characteristics of our present devices are shown in Fig. 4, which plots the V<sub>D</sub> dependence of  $I_D$ ,  $I_C$ , and  $g_m$  at a fixed collector bias  $V_C = 5.0 \,\mathrm{V}$ . We see that in a narrow range of V<sub>D</sub> above 1 V the injection current rises by an order of magnitude, leading to an extremely high  $g_{\rm m} = 23.1$  S/mm. When the injection current exceeded certain limit (≈50 mA for 25 µm devices), the InAlAs barriers usually suffered a dielectric

Figure 4: Drain current,  $I_{\rm D}$ , collector current  $I_{\rm C}$ , and the transconductance  $g_{\rm m}$  as functions of the drain voltage at a high collector bias  $V_{\rm C}$ =5.0 V [14]. Large enhancement in the transconductance is observed at  $V_{\rm D} > V_{\rm NDR}$  in the stable NDR region. Diamonds represent the actual discrete data points for  $g_{\rm m}$  in that region obtained by a numerical differentiation of the  $I_{\rm C}$  curve.

breakdown. Therefore, we had to limit the  $I_{\rm C}$ : the data presented in Fig. 3 were collected with a compliance set at 40 mA. The large boost in the injection current is observed within a range  $V_{\rm D}=1.02-1.03\,{\rm V}$  right after  $V_{\rm NDR}$ , but before the onset of circuit oscillations caused by the NDR. The existence of a stable NDR region has been observed only at large values of  $V_{\rm C}$ . The measured characteristics in the narrow range of ultra-high  $g_{\rm m}$  are highly reproducible with no sign of hysteresis.

In Ref. [14], the ultra-high  $g_m$  was attributed to the formation of a high-field RST domain in the channel. In a narrow range of  $V_D$ , corresponding to the stable NDR, the source-to-drain electric field (initially, relatively uniform over the channel because of the high carrier concentration) concentrates in a "hot spot" (the domain) depleted of carriers. The idea of an abrupt global charge redistribution in the device is supported by Monte Carlo studies of the CHINT/NERFET [25]. It was suggested [14] that at high values of  $V_C$  the domain formation may occur continuously as a function of  $V_D$ . In this picture, a small variation of VD would reduce the domain size, thus producing a large change in the electric field, hence a large variation in  $T_e$  and  $I_C$  that gives rise to a high  $g_m$ .

It should be noted, however, that there is another possibility to explain the ultra-high  $g_m$ ,

namely avalanche multiplication by impact ionization. At this time, I consider this possibility more likely to be correct than the one suggested earlier [14]. Indeed, the very magnitude of the current observed in the high- $g_{\rm m}$  region can hardly be explained without an avalanche gain. The maximum injection current without avalanche can be estimated from the highest possible channel concentration, limited by the dielectric strength  $E_{\rm br}$  of the barrier:

$$W^{-1}I_{\rm C}^{\rm max}=\varepsilon E_{\rm br}\,v,$$

where  $\varepsilon$  is the dielectric permittivity in the barrier and v an effective high-field velocity in the emitter channel prior to RST. Taking  $\varepsilon E_{\rm br}/e \approx 10^{12} \, {\rm cm}^{-2}$ and assuming the peak scattering-limited velocity in InGaAs [27],  $v \approx 2 \times 10^7 \text{ cm/s}$  $W^{-1}I_C^{\text{max}} \approx 3 \text{ A/cm}$ . This is to be compared with the data in Fig. 4, corresponding to  $W^{-1}I_{C}^{max}$  of nearly 20 A/cm. While it cannot be excluded that the transient electron velocity in the channel strongly overshoots the scattering-limited value, it is much more likely that we are dealing with an avalanche gain. The device thus operates similar to an avalanche photodiode, with the RST current providing the primary carriers that initiate avalanche. This mode of operation may be beneficial in applications requiring high injection current.

# 4. CHARGE INJECTION LOGIC

The fact that the RST current  $I_{\rm C}$  does not depend on which of the two surface terminals, S or D, is chosen to be the source, allows the implementation of devices in which the role of a particular terminal in the circuit is not defined by the layout.

Consider the circuit illustrated in the top portion of Fig. 5 not as a transistor but as a logic element with inputs S and D corresponding to the biases on the S and D electrodes, respectively. The point to note is that the logic function OUT(S,D) represents an exclusive NOR, since OUT is high when  $I_C$  is low (no RST) and OUT is low when the injection current is flowing. The latter situation results only when the voltages S and D are sufficiently different.

The bottom part of figure 5 illustrates a schematic diagram of the proposed logic element NORAND which has three logic inputs  $X_j$  (j=1,2,3) and one output OUT. Which of the  $X_j$  will serve as a source and which as a drain is determined only at the time when a particular logic operation is performed. The value of OUT is high (logic 1) is only when all three  $X_j$ 's have same

Figure 5: Schematic illustration of the charge injection logic. Top figure on the right introduces a circuit symbol of the CHINT. The bottom figures illustrate the NORAND element. Figure on the bottom left describes a symmetric arrangement of three identical channels,  $X_{3-1}$ ,  $X_{1-2}$ , and  $X_{2-3}$ . By symmetry, one has the same amount of hot-electron injection for any of the six states of binary input in which at least one of the three  $X_j$ 's is different from the other two. The bottom figure describes an asymmetric NORAND layout. One of the electrodes is physically (but not logically) split, resulting in a "periodic" boundary condition, equivalent to the three-fold rotational symmetry of the left figure.

value (high or low). All the other six possible logic input configurations lead to the same high injection current resulting from hot electron emitters formed in two of the three channels,  $X_{3-1}$ ,  $X_{1-2}$ , and  $X_{2-3}$ . Three of these configurations correspond to the presence of two sources and one drain, the other three to one source and two drains.

It is easy to see that the logic function  $OUT({X_i})$  is given by

$$(X_1 \cap X_2 \cap X_3) \cup (\overline{X}_1 \cap \overline{X}_2 \cap \overline{X}_3),$$

where the symbols  $\bigcap$ ,  $\bigcup$ , and  $\overline{A}$  stand for logic functions AND, OR, and NOTA, respectively. The truth table of the NORAND is as follows:

|                         | I                         |   | II    |   |   | Ш              |   | IV    |  |

|-------------------------|---------------------------|---|-------|---|---|----------------|---|-------|--|

| <b>X</b> <sub>1</sub> : | 0                         | 0 | 1     | 1 | 0 | 0              | 1 | 1     |  |

| <b>X</b> <sub>2</sub> : | 0                         | 1 | 0     | 1 | 0 | 1              | 0 | 1     |  |

| X <sub>3</sub> :        | 0                         | 0 | 0     | 0 | 1 | 1              | 1 | 1     |  |

| OUT:                    | 1                         | 0 | 0     | 0 | 0 | 0              | 0 | 1     |  |

|                         | $\overline{X_1 \cup X_2}$ |   | (NOR) |   | x | $X_1 \cap X_2$ |   | (AND) |  |

We see that the NORAND operates as a NOR  $(X_1, X_2)$  when the input to  $X_3$  is low, and as an

AND  $(X_1, X_2)$  when  $X_3$  is high. It is clear that the three-fold symmetry of the device ensures that the injection current has the same value in all the six states corresponding to logic OUT=0. Of course, one can achieve a similar effect without an exact three-fold symmetry, e.g. with a "cylindrically" symmetric arrangement of the  $\{X_j\}$  electrodes, as illustrated in the bottom right part of Fig. 5.

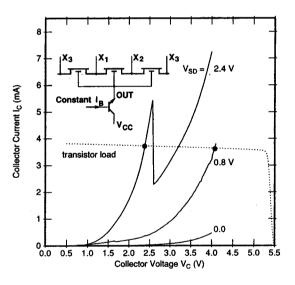

The operation of NORAND has been demonstrated [12] with a circuit consisting of three discrete CHINT devices with similar characteristics. The circuit, shown in the insert to Fig. 6, is functionally equivalent to a monolithic structure with three input terminals. The common-source characteristics of one of these devices are shown in Fig. 6. For the load device we took a transistor used as a nearly constant current source, see the dotted line in Fig. 6.

**Figure 6:** Common-source characteristics of one of the devices forming a composite NORAND element [12]. Collector current  $I_C$  is plotted against the collector voltage  $V_C$  with the heating voltage  $V_D$  as a parameter. Dotted line indicates the load curve for a transistor load used in the demonstration. The circuit connection is shown schematically in the insert.

The reason we had to use a high-impedance load is instructive. For a meaningful demonstration the device should, of course, operate with a logic gain. In switching a single device, the gain equals  $\bar{g}_m R_L$ , where  $R_L$  is the load resistance and  $\bar{g}_m$  the

average transconductance in the bias range corresponding to the switching However, because of the unavoidable slight differences between the devices it was inconvenient to operate within the narrow range of high  $g_m$ . Another, more critical, difficulty was associated with the fact that each emitting channel,  $X_{i-j}$ , i, j = 1, 2, 3, should, ideally, be stable against oscillations in the input circuit, i.e., the logic state corresponding to a high value of  $|X_i-X_i|$  should be outside the NDR region of the  $I_D(V_D)$ characteristic. Experimentally, at high V<sub>C</sub> the NDR region typically spans about 1.5 to 3.5 V, cf. Fig. 3. This feature is undesirable because it implies that in order to obtain a voltage gain, one would have to use a high load resistance. However, the wide extent of the unstable region appears to be related to the interaction between the active device and the reactive impedances of an external circuit. The NDR region becomes narrower for devices with smaller channel widths.

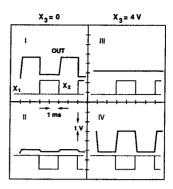

For the purpose of illustration, we ensured the circuit stability by performing the switch in a range of relatively low average transconductance  $\bar{g}_m$  and employing a high-impedance load. The measured functional characteristics of the circuit showed logic gain in reproducing the NORAND truth table. These characteristics are illustrated in Fig. 7. The two traces on the left correspond to  $X_3=0$  and illustrate the operation of NOR( $X_1, X_2$ ); the traces on the right correspond to  $X_3=4V$  and the operation of AND( $X_1, X_2$ ). The order of traces agrees with that in the truth table: e.g., the bottom trace on the right illustrates the last two columns of the table.

In order that a logic device could be used in integrated circuits, it is necessary that its input and output voltages be consistent. As Fig. 7 suggests, in the case of NORAND this may require an additional level-shifting circuitry. In principle, this would not be a necessary requirement if only the NOR part of the NORAND truth table were to be employed. In the NOR configuration, the device has a well-defined ground level, and a consistent range of input-output characteristics can be found, as we have ascertained experimentally. On the other hand, in the AND configuration the low-OUT voltage must be higher than the lowest of the input voltages. In an optimized device, this difference can be made small, but since it would still accumulate after several stages, the level shifting will be mandatory. Of course, it is well-known that all logic functions can be implemented on the basis of a NOR element alone.

Figure 7: Experimental illustration of the operation of a NORAND element assembled from three discrete CHINT devices with similar characteristics (as in Fig. 6): oscilloscope traces of the NORAND response function. Dashed lines correspond to  $X_1$ , thin solid lines to  $X_2$ , and heavy lines to OUT. Traces I and II were obtained with  $X_3 = 0$ ; traces III and IV correspond to  $X_3 = 4$ V. Each quadrant in the figure illustrates two columns of the NORAND truth table with the roman numerals corresponding to those in the table. All traces refer to an origin at the bottom left corner in each of the four quadrants.

The NORAND functional element departs radically from all previously contemplated uses for multiterminal RST devices [26]. At the same time, it represents a natural embodiment of the essence of hot-electron injection by the RST. Compared to all existing logic families, the NORAND offers a considerable economy in the layout of basic functional elements. Moreover, it promises faster operation of these elements, since the entire function is implemented within one gate delay of a high-speed transistor.

#### 5. MICROWAVE STUDIES OF CHINT

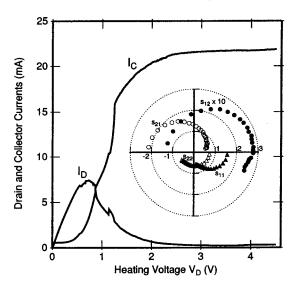

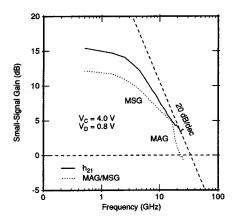

High-frequency characterization has been reported for CHINT devices implemented in GaAs/AlGaAs heterostructures [10] and, recently, for a novel three-terminal RST device in a strained-layer InGaAs/AlGaAs/GaAs heterostructure Microwave studies of In<sub>0.53</sub>Ga<sub>0.47</sub>As/In<sub>0.52</sub>Al<sub>0.48</sub>As transistors have just began with the preliminary results reported in Ref. [20]. In these studies, the CHINT devices of the variety described in Sect. 2 were characterized on-wafer at room temperature in a frequency range 0.5-25.5 GHz. The smallsignal current gain  $(h_{21})$  and power gain parameters (MAG/MSG) were calculated from the measured S-parameters and plotted scattering frequency for a number of DC biasing conditions.

Figure 8: Static *I-V* characteristics at  $V_{\rm C}$ =4.0 V and the scattering parameters measured for the same device at  $V_{\rm C}$ =4.0 V and  $V_{\rm D}$ =0.8 V. Device geometry: W=25 µm,  $L_{\rm ch}$ =0.8 µm. The S-matrix data are plotted in the complex plane for frequencies ranging from 0.5 to 25.5 GHz. After Ref. [20].

Figure 8 displays both the static characteristics and the S-parameter data for the same device. The static measurement was obtained prior microwave testing using low-inductance probes. The low-inductance probes substantially reduce the circuit oscillations at low frequencies caused by the NDR in the drain circuit. The microwave data presented in Fig. 8 correspond to a region immediately following the onset of NDR in the drain characteristic. Compared to bipolar or fieldeffect transistors, the scattering parameters of show several unusual features. particular,  $\arg(S_{12}) \to \pi$  in the DC limit, which may indicate the existence of a positive feedback. Also, the magnitude of the input reflection coefficient  $|S_{11}|$  can be larger than unity due to the NDR in the input circuit. On the other hand, the behavior of  $S_{21}$  and  $S_{22}$  shows no apparent anomalies.

The calculated small-signal current gain,  $h_{21}$ , and the maximum available gain (MAG) are plotted in Fig. 9 for the same DC bias as in Fig. 8. In the range of frequencies where Rollet's factor K is less than unity, the maximum stable gain (MSG) was calculated instead of MAG. At these frequencies, the device is potentially unstable. Since in the range where MAG exists (K>1) it equals

Figure 9: Small-signal gain parameters calculated from the S-parameters displayed in Fig. 8.

MSG× $[K-(K^2-1)^{1/2}]$ , the composite MSG/MAG curves exhibit a kink near K=1. For some bias conditions, the device is unstable up to the highest measured frequencies and the corresponding curves exhibit no kink [20].

In general, the high-frequency roll-off of the gain parameters in our device had a slope smaller than 20 dB/decade. Extrapolating at 20 dB/decade we found that the highest unity-current-gain frequency is slightly above 40 GHz. The maximum oscillation frequency,  $f_{max}$ , is difficult to obtain for bias points where MAG does not exist within the measurement range, i.e. if K < 1 for  $f \le 25.5$  GHz. However, for some DC bias conditions, e.g. at  $V_D$ =1.10 V and  $V_C$ =4.5 V, the device still oscillates (K=0.68) at  $f=25\,\text{GHz}$ . Extrapolating from the frequency dependence of the K-factor, we found that  $K \rightarrow 1$  at  $f \approx 35$  GHz, which gives an estimate for the  $f_{max}$  in our device. The measured gain cutoff frequencies exceeded  $\sim 20\,\mathrm{GHz}$  in a range of  $V_\mathrm{D}$  at least  $0.5 \,\mathrm{V}$  wide and a still wider range of  $V_{\mathrm{C}}$ .

The charge injection transistor is attractive for its high speed electronics since performance is believed to be limited only by the time of flight of hot electrons across the barrier layer (another delay associated with the time required for the electron scattering to establish an effective temperature in the emitter channel is expected to be shorter than 1 ps). For our present device with a 2000 A thick barrier the transit time can be estimated to be between 2 and 3 ps. This would mean an  $f_T$  between 50 and 80 GHz. Inasmuch as the bandwidth of our devices is below this fundamental limitation, it is likely that the RC

delay associated with the parasitic drain-to-collector capacitance is still responsible for limiting the device speed, just as it was the case for devices used in earlier microwave studies [10].

One obvious avenue for improvement is to minimize the drain area. However, since the transit time decreases while the RC delay increases with diminishing barrier thickness, the drain-tocollector capacitance will always remain a factor to be concerned about. A promising direction is to use for the barrier layer semiconductors like InP where the electronic transport is faster. interesting alternative approach was recently reported by Hueschen et al. [17]. These authors studied an RST transistor, very similar in concept to CHINT, but with an inverted structure in which the collector is the top layer. This allows to reduce the drain-collector capacitance, which has probably contributed to the higher current-gain cutoff frequency ( $f_T = 60 \,\text{GHz}$ ) found in ref. [17].

#### 6. CONCLUSION

We have reviewed recent progress in the implementation and characterization of charge injection transistors as well as their possible use in logic circuits. It is clear that the InGaAs/InAlAs heterostructure lattice-matched to InP is an excellent material system for the implementation of real-space transfer transistors. However, the use of InP itself for the barrier layer is expected to yield improvements in microwave performance.

Static characteristics of InGaAs/InAlAs CHINT/NERFET devices are quite striking, with the peak-to-valley ratio in the NDR exceeding 7,000 and the CHINT transconductance reaching 20 S/mm. Studies of charge injection in these devices are expected to bring forth new information about the physics of hot-electron transport in heterostructures. It is clear that future research on charge injection transistors must be focussed on their intended applications. Perhaps the most interesting recent accomplishment related to the proposal and experimental CHINT is demonstration of a new logic element, called the The demonstrated fact that this element can perform both AND and NOR functions, reprogrammable with the characteristic CHINT speed in the course of computation, represents unique property of charge injection by real-space transfer.

Acknowledgement - I wish to thank A. Y. Cho, P. A. Garbinski, P. M. Mensz, M. R. Pinto, and

D. L. Sivco for their contributions to the work reviewed here.

#### REFERENCES

- A. Kastalsky and S. Luryi, "Novel Real-Space Hot-Electron Transfer Devices", IEEE Electron Device Letters EDL-4, 334 (1983).

- S. Luryi, A. Kastalsky, A. C. Gossard, and R. H. Hendel, "Charge Injection Transistor Based on Real-Space Hot-Electron Transfer", IEEE Transactions on Electron Devices ED-31, 832 (1984).

- A. Kastalsky, S. Luryi, A. C. Gossard, and R. Hendel, "A Field-Effect Transistor with a Negative Differential Resistance", *IEEE Electron Device Letters* EDL-5, 57 (1984).

- K. Hess, H. Morkoç, H. Shichijo, and B. G. Streetman, "Negative differential resistance through real-space electron transfer," Applied Physics Letters 35, 469 (1979).

- Z. S. Gribnikov, "Negative differential conductivity in a multilayer heterostructure," Fizika i Tekhnika Poluprovodnikov 6, 1380 (1972) [Soviet Physics -Semiconductors 6, 1204 (1973)].

- M. Keever, H. Shichijo, K. Hess, S. Banerjee, L. Witkowski, H. Morkoç, and B. G. Streetman, "Measurements of hot-electron conduction and real-space transfer in GaAs/AlGaAs heterojunction layers," *Applied Physics Letters* 38, 36 (1981).

- K. Hess, "Principles of hot electron thermionic emission (real space transfer) in semiconductor heterolayers and device applications," Festkörperprobleme 25, 321 (1985).

- S. Luryi and A. Kastalsky, "Hot electron injection devices", Superlattices and Microstructures 1, 389 (1985).

- S. Luryi and A. Kastalsky, "Hot-Electron Transport in Heterostructure Devices", *Physica* 134-B, 453 (1985).

- A. Kastalsky, J. H. Abeles, R. Bhat, W. K. Chan, and M. Koza, "High-Frequency Amplification and Generation in Charge Injection Devices", *Applied Physics Letters* 48, 71 (1986).

- A. Kastalsky, "Novel real-space transfer devices", in *High-Speed Electronics*, ed. by B. Källbäck and H. Beneking (Springer-Verlag, Berlin, 1986) pp. 62-71.

- S. Luryi, P. Mensz, M. Pinto, P. A. Garbinski, A. Y. Cho, and D. L. Sivco, "Charge Injection Logic", Applied Physics Letters 57, 1787 (1990).

- P. M. Mensz, S. Luryi, A. Y. Cho, D. L. Sivco, and F. Ren, "Real Space Transfer in Three-Terminal InGaAs/InAlAs Heterostructure Devices", Applied Physics Letters 56, 2563 (1990).

- P. M. Mensz, P. A. Garbinski, A. Y. Cho, D. L. Sivco, and S. Luryi, "High Transconductance and Large Peak-To-Valley Ratio of Negative Differential Conductance in Three-Terminal InGaAs/InAlAs Real-Space Transfer Devices", Applied Physics Letters 57, December 10 (1990).

- M. E. Favaro, G. E. Fernández, T. K. Higman, P. K. York, L. M. Miller, and J. J. Coleman, "Strained layer InGaAs channel negative-resistance field-effect transistor" *Journal of Applied Physics* 65, 378 (1989).

- M. E. Favaro, J. J. Alwan, R. P. Bryan, L. M. Miller, J. J. Coleman, J. Kim, and C. M. Wayman, "Strained Layer AlGaAs-GaAs-InGaAs Real-Space Transferred Electron Devices", *Electronics Letters* (1990).

- M. R. Hueschen, N. Moll, and A. Fischer-Colbrie, "Improved Microwave Performance in Transistors Based on Real-Space Electron Transfer", Applied Physics Letters 57, 386 (1990).

- M. E. Favaro, L. M. Miller, R. P. Bryan, J. J. Alwan, and J. J. Coleman, "p-channel negative resistance field-effect transistor", Applied Physics Letters 56, 1058 (1990)

- P. M. Mensz, S. Luryi, J. C. Bean, and C. J. Buescher, "Evidence for a Real-Space Transfer of Hot Holes in Strained GeSi/Si Heterostructures," Applied Physics Letters 56, 2663 (1990).

- P. M. Mensz, H. Schumacher, P. A. Garbinski, A. Y. Cho, D. L. Sivco, and S. Luryi, "Microwave operation of InGaAs/InAlAs charge injection transistors", 1990-IEDM Technical Digest (1990).

- A. A. Grinberg, A. Kastalsky, and S. Luryi, "Theory of hot electron injection in CHINT/NERFET devices," IEEE Transactions on Electron Devices ED-34, 409 (1987).

- M. Mosko, I. Novak, and R. Quittner, "On the analytical approach to the real-space transfer in GaAs-AlGaAs heterostructures", Solid-State Electronics 31, 363 (1988).

- M. Mouis, F. Paviet-Salomon, P. Dollfus, and R. Castagné, "Real-Space Transfer in Heterojunction FETs: Monte-Carlo Simulation and Analytical Model", Journal of Physics (Paris) Colloq. 49, C-4, 567 (1988).

- I. C. Kizilyalli, K. Hess, T. Higman, M. Emanuel, and J. J. Coleman, "Ensemble Monte Carlo simulation of real space transfer (NERFET/CHINT) devices," Solid-State Electronics 31, 355 (1988).

- I. C. Kizillyalli and K. Hess, "Physics of Real-Space Transfer Transistors", Journal of Applied Physics 65, 2005 (1989).

- S. Luryi, "Hot-Electron Injection and Resonant-Tunneling Heterojunction Devices," Chap. 12 in Heterojunction Band Discontinuities: Physics and Device Applications, ed. by F. Capasso and G. Margaritondo (Elsevier Science Publishers B. V., Amsterdam, 1987) pp. 489-564.

- Landolt-Borstein Tables, ed. by O. Madelung, H. Schulz, and H. Weiss (Springer, Berlin, 1982) and GaInAsP Alloy Semiconductors, ed. by T. P. Pearsall (Wiley, New York, 1982).

- 28. This effect is similar to the distortion of a hotdistribution function K. Hess. electron "Phenomenological physics of hot carriers in semiconductors", in Physics of Nonlinear Transport in Semiconductors, ed. D. K. Ferry, J. R. Barker, C. Jacoboni, (Plenum Publishing Corporation, 1980)] above the optical-phonon threshold at low densities of the electron gas (below approximately 10<sup>17</sup> cm<sup>-3</sup>). With the reduced electron-electron collision rate, the high-energy tails of the distribution can be strongly depressed - compared to a Maxwellian curve - because of the emission of optical phonons. For 2D electronic systems this effect has been discussed by S. E. Esipov and I. B. Levinson, "Electron temperature in a twodimensional gas: energy losses to optical phonons," Zhurnal Eksperimental'noi i Teoreticheskoi Fiziki 90, 330 (1986) [Soviet Physics - JETP 63, 191 (1986)].