# Active Packaging: a New Fabrication Principle for Ultra-High Performance Components and Systems

## Serge Luryi

AT&T Bell Laboratories, Murray Hill, NJ 07974 USA

#### Introduction

In this work I shall discuss a new device fabrication principle which I would like to refer to as *active packaging* (AP). The meaning of this term is that certain essential fabrication steps (lithography, etching, metallization, etc.) are performed *after* the partially processed device or circuit is packaged onto a host platform. In many instances, AP enables the implementation of structures that cannot be realistically obtained in another way, such as those requiring lithography on *opposite* sides of a thin semiconductor film.

One of the most important goals of the AP concept is the combination of dissimilar materials (notably, III-V compound semiconductors) with silicon integrated circuitry (IC) on a single Si substrate. This goal, now widely recognized as an important research direction in microelectronics, is shared by other emerging technologies, such as those based on *heteroepitaxial* and *thin-film transfer* techniques. At the same time, AP *widens* significantly the class of device structures that can be manufactured. Our ultimate goal is not only to "teach the old dog new tricks" but also to greatly expand the assortment of tricks available.

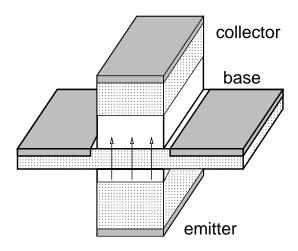

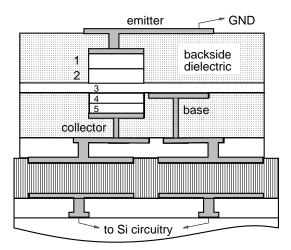

The concept of active packaging will be illustrated by a process resulting in the formation of a heterostructure bipolar transistor (HBT) structure, schematically shown in Fig. 1. The AP HBT structure reduces the parasitic capacitance between the base and the collector electrodes, enabling the ultrafast performance with the maximum oscillation frequency in the range of 300-400 GHz and even higher. This opens up the possibility of implementing on-chip millimeter-wave phased-array antenna systems.

Fig. 1. Idealized cross-section of a heterostructure bipolar transistor to be fabricated by active packaging. Dotted indicates the conducting (undepleted) layers, shaded pattern the contact metal. The emitter and collector stripes are defined independent lithographic steps and aligned to each other. If the upward direction is defined as that outward from the surface on which the lithography is performed, then both the emitter and the collector can be considered "up".

### **Active Packaging HBT Process**

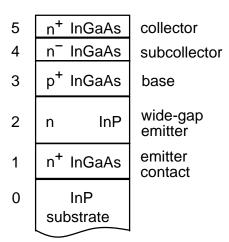

The process is based on flip-chip packaging, removal of the substrate, and backside lithography. Fabrication begins with an epitaxial structure of the following composition:

**Fig. 2.** Epitaxial structure of InGaAs/InP HBT to be fabricated by active packaging. The emitter contact layer 1 is also an etch stop for InP. For etch-stop reliability it may be convenient to include a pair of sacrificial InP-on-InGaAs layers between layers 0 and 1, so that the etching is performed in steps and results in uncovering an ideal flat surface of the emitter contact.

Top side processing. No attempt is made at this stage to contact the emitter. Top side processing includes etching of the collector stripe down to the base layer, evaporation and alloying of self-aligned contacts to the base, deposition of a passivating dielectric, etching of via holes in the dielectric, and final metallization. The final metal connects different devices in a circuit that has a relatively small number of communication points with the outside world. The circuit is then covered by another ("interlevel") dielectric layer and the communication points are connected to "top" metal pads through a second set of via holes. The top pads may be relatively wide (e.g.,  $\geq 100~\mu m$ ). The interlevel dielectric (e.g., polyimyde) may be planarized. After the top-side processing all the base and collector contacts are connected in a circuit with lines running over the passivating dielectric. Selected circuit points are connected with top metal pads through via holes in the interlevel dielectric. Emitter layers are not yet contacted.

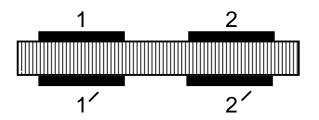

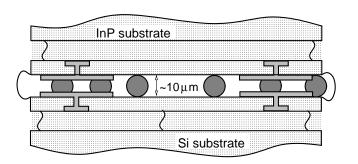

Flip-chip mount; "consulator" film. The circuit is then mounted on a "carrier" wafer which has a mirror pattern of top-metal electrodes. The carrier may be any substrate, including glass, ceramics, etc., but first and foremost a silicon wafer that has already undergone the integrated circuit processing. Connection between overlapping metallic pads is established with the help of an anisotropically conducting film with electrical properties, illustrated in Fig. 3. The film must provide a short between overlapping contacts and an open circuit otherwise. The minimum required overlap area and distance between non-overlapping electrodes should not be too large, preferably less than 100  $\mu m$ . Such vertically conducting and laterally insulating films, which may be called "consulators", can be prepared in a variety of ways. The primary purpose of the consulator, besides providing vertical electrical connections, is to provide a stable mechanical support for the packaged chip – support that will become crucial when the InP substrate is removed.

**Fig. 3.** Required "consulator" film. For overlapping electrodes the film provides a short,  $R(11') \approx R(22') \leq 10 \,\Omega$ , while nonoverlapping electrodes form an open circuit,  $R(12) \approx R(12') \geq 10^8 \,\Omega$ .

In principle, a perfectly adequate consulator can be provided by the solder-bump technology. One needs an adhesive dielectric that can flow to fill the narrow spacing between the chip and the carrier wafer and then stiffen to provide the necessary mechanical support. Another possible approach is to use the existing packaging technology of anisotropically conductive adhesive films, used in liquid crystal display assemblies. These materials are not intrinsically anisotropic, they conduct in a preferred direction only after having been processed, Fig. 4.

Fig. Anisotropically conductive adhesives (after Ref. 3). Small conducting spheres are dispersed in an epoxy matrix at a concentration far below the percolation The assembly is compressed threshold. until hard spheres touch both surfaces (extra epoxy oozes out). **Electrical** connection is established only vertically, since neighboring spheres rarely touch.

Substrate removal and back-side processing. It is quite possible to etch the entire InP substrate down, stopping at a  $0.1~\mu m$  InGaAs layer. This step is based on the well-known extreme selectivity between the etch rates for InP and InGaAs in hydrochloric acid solutions. It is essential that the uncovered surface of layer 1 is uniformly flat, adequate for performing a fine line optical lithography. A large hole etched from the substrate side would not do, because there would be problems with focal depth.

To make lithographic alignment to the base contact level, the contact metal should be seen with a sufficient contrast through layers 1-3. If this proves to be inconvenient, then special topography features for the back-side alignment must be provided at the top-side processing stage.

The emitter contact is established by a standard lift-off evaporation of a suitable metal. It is well known that ohmic contacts to  $n^+$  InGaAs are good without alloying. No elevated temperature procedures should be contemplated after the chip has been mounted, because of the limited thermal stability that can be expected of a consulator film and the need to preserve the integrity of fully processed Si integrated circuits on the carrier wafer.

Fig. 5. Cross-section of the final assembly after active packaging. Emitter stripe is aligned to and slightly overlaps the collector stripe. It is assumed for simplicity that all HBT's are used at common emitter, so that the emitter final metal is connected to the ground of the Si circuit. Of course, this may not be true in general, and the emitter final metal pattern may be more complicated. Connection to the rest of the circuit may go across the periphery of the chip, or via the consulator film.

### **Advantages**

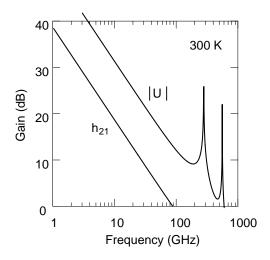

The reduced base-collector capacitance offers significant advantages for microwave performance of HBT. An enhancement of the maximum oscillation frequency  $f_{\rm max}$  by a factor of 2 to 3 has been predicted<sup>4,5</sup> over optimized collector-down structures. Moreover, with a suppression of the extrinsic collector capacitance  $C_{\rm Cx}$  it becomes possible to implement HBT structures with coherent effects in the base,<sup>6,7</sup> resulting in a power gain above the conventional cutoff frequencies. Figure 6 shows the modeled microwave characteristics of C-up HBT, in which the base bandgap is graded so that the total base propagation delay  $\tau$  is much shorter than the diffusive delay in a flat base of the same width.<sup>7</sup> The magnitude of the base transport factor  $\alpha = |\alpha| \exp(-2\pi i f \tau)$  decreases so slowly with increasing frequency f that it becomes feasible to activate transit-time resonances far above  $f_{\rm T} \approx 1/2\pi\tau$ .

**Fig. 6.** Common-emitter current gain  $|h_{21}|$  and the unilateral gain |U| of a model HBT whose base bandgap narrows down toward the collector in N=5 discontinuous steps (after Ref. 7). Base total width is  $W=0.25~\mu \mathrm{m}$  and the minority carrier diffusivity  $D=50~\mathrm{cm}^2/\mathrm{s}$ . The collector transit time  $\tau_C=1~\mathrm{ps}$ . Transistor is assumed loaded with the parasitics with standard equivalent circuit parameters, except  $C_{\mathrm{Cx}}$  assumed negligible.

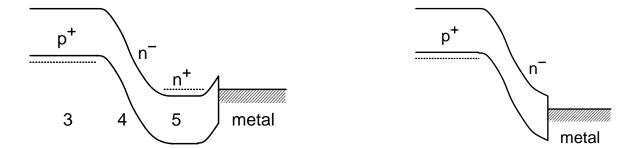

**Fig. 7.** Illustration of a conventional ohmic semiconductor-metal contact (a) and a Schottky collector (b). Numbers in (a) refer to the layer labeling scheme in Fig. 2. In a Schottky-collector device, layer 5 would be eliminated altogether and a suitable metal deposited directly on the lightly-doped layer 4, completely depleted of mobile carriers.

An interesting further advantage of an inverted HBT is the possibility of accommodating a Schottky collector, Fig. 7. An important parasitic resistance in small area devices is due to the metal semiconductor junction. Since the resistance of an ohmic contact scales with its area, at small enough dimensions it must dominate other resistances that scale with the contact perimeter. It therefore makes sense to dispense with the  $n^+$  doped semiconductor layer in the collector (layer 5 in Fig. 2). Such an approach has been successfully used in the fabrication of submicron resonant tunneling diodes. The high thermal conductivity of a metallic layer and its proximity to the  $n^-$  base-collector field region, where most of the heat is generated, is another important advantage of a Schottky collector. Needless to say, a Schottky collector is realistic only in the C-up configuration. Its implementation is entirely compatible with the AP process.

# **Applications**

Based on AP HBT technology it is entirely feasible to implement local oscillators and amplifiers that operate at millimeter and even submillimeter wavelengths. One obvious application of such devices would be for satellite communication systems in the atmospheric transmission window of 345 GHz.

Another extremely attractive application is the possibility of fabricating millimeter-wave *phased arrays on a silicon chip.* A  $\lambda 2$  spaced linear array of 20 elements radiating at 300 GHz would be about a centimeter long. The advantage of having transistor oscillators is that the millimeter-wave beam can be electrically steered off broadside by controlling the relative amplitudes of different oscillators, while their relative phases are locked together by the evanescent wave interaction. The point is that most available phase shifters used in centimeter wave phased array systems are bulky elements that cannot be used in on-chip designs. Instead, we should use electronic beam steering by controlling the *amplitude* of constant-phase array elements. As far as I am aware, this idea has not been employed in practical phased-array antenna systems, perhaps because at centimeter wavelengths it is more efficient to control the relative phases of array elements. In the millimeter and submillimeter wavelength range amplitude steering appears to be the only realistic

way to implement purely electronic beam steering. Three-terminal devices are ideally suited for this purpose. On-chip focal plane antenna arrays should have important applications as steerable radar systems in avionics, automated manufacturing, and especially in automobile collision avoidance and early warning systems.

It is clear that the AP will make possible the implementation of other new devices and circuits that would not be feasible without this new technology. I believe that most significant applications of compound semiconductor electronics will be associated with its use in silicon electronics. In terms of the old debate on Si vs GaAs, my view is that silicon is the ultimate customer for GaAs. The logic of industrial evolution will motivate new paths for a qualitative improvement of system components, other than the traditional path of a steady reduction in fine-line feature size. The principle of active packaging, illustrated in the present work using the instance of implementing ultra-high performance InP HBT on a silicon chip, will become one of the central design principles of future microelectronics.

#### References

- 1. S. Luryi and S. M. Sze, "The Future of Microelectronics Hybrid Material Systems of IV/III-V Compound Semiconductors", *AT&T Bell Laboratories Tech. Memorandum* 52111-840920-01, Sept. 1984; "Possible device applications of silicon molecular beam epitaxy", in *Silicon Molecular Beam Epitaxy*, ed. by E. Kasper and J. C. Bean, Vol. 1, Chap. 8 (CRC Uniscience Press, Inc., 1988) pp. 181-240.

- 2. J. Deboeck and G. Borghs, "III-V on Si heteroepitaxy versus lift-off techniques", *J. Cryst. Growth* **127**, pp. 85-92 (1993).

- 3. A. M. Lyons and D. W. Dahringer, "Electrically Conductive adhesives", in *Handbook of Adhesives Technology*, K. Mittal and A. Pizzi, Eds., (Marcel Dekker, New York, 1993).

- 4. H. Kroemer, "Heterostructure bipolar transistors and integrated circuits", *Proc. IEEE* **70**, pp. 13-25 (1982).

- C. G. Fonstad, "Consideration of the relative frequency performance potential of inverted heterojunction n-p-n transistors", *IEEE Electon Dev. Lett.* EDL-5, pp. 99-100 (1984).

- 6. A. A. Grinberg and S. Luryi, "Coherent Transistor", *IEEE Trans. Electron Devices* **ED-40**, pp. 1512-1522 (1993).

- 7. S. Luryi, A. A. Grinberg, and V. B. Gorfinkel, "Heterostructure bipolar transistor with enhanced forward diffusion of minority carriers", *Appl. Phys. Lett.* **63**, pp. 1537-1539 (1993).

- 8. S. Allen, M. Reddy, M. Rodwell, R. Smith, J. Liu, S. Martin and R. Muller, "Submicron Schottky-collector AlAs/GaAs resonant tunnel diodes", 1993-IEDM *Tech. Digest*, pp. 407-410 (1993).

- 9. J. P. Costas, "An antenna beam steering technique comprised of constant-phase array elements", *Proc. IEEE* **69**, pp. 745-747 (1981).