### Enhancing Power and Signal Integrity in Three-Dimensional Integrated Circuits

A Dissertation Presented

by

### Hailang Wang

to

The Graduate School

in Partial Fulfillment of the

Requirements

for the Degree of

### **Doctor of Philosophy**

in

### **Electrical Engineering**

Stony Brook University

May 2016

#### **Stony Brook University**

The Graduate School

### Hailang Wang

We, the dissertation committee for the above candidate for the Doctor of Philosophy degree, hereby recommend acceptance of this dissertation.

### Dr. Emre Salman - Dissertation Advisor Assistant Professor, Department of Electrical and Computer Engineering

### Dr. Sangjin Hong - Chairperson of Defense Professor, Department of Electrical and Computer Engineering

Dr. Milutin Stanacevic - Defense Committee Member Associate Professor, Department of Electrical and Computer Engineering

### Dr. Thomas MacCarthy - Defense Committee Member Assistant Professor, Department of Applied Mathematics and Statistics

This dissertation is accepted by the Graduate School

### Charles Taber Dean of the Graduate School

#### Abstract of the Dissertation

### Enhancing Power and Signal Integrity in Three-Dimensional Integrated Circuits

by

#### Hailang Wang

**Doctor of Philosophy**

in

**Electrical Engineering**

Stony Brook University

2016

Three-dimensional (3D) integration has emerged as an enabling technology for integrated circuits (ICs) in the interconnect-centric design era, where the interconnects have become a bottleneck for the overall system performance. With 3D integration technology, multiple planar dies are stacked vertically while the communication among different dies is achieved by low impedance vertical connections such as through silicon vias (TSVs) or monolithic inter-tier vias (MIVs). Due to the unique characteristics of 3D ICs, various challenges exist in the fabrication, design and testing of 3D integrated systems. The research work proposed in this dissertation is focused on 3D design methodologies with emphasis on power and signal integrity.

Specifically, to reliably deliver the power supply voltage to each circuit mod-

ule within a 3D system, *i.e.*, maintaining system-wide power integrity, the power distribution network in 3D ICs should be carefully designed with specific design considerations different from traditional 2D ICs. In this dissertation, two critical issues about the power distribution network are investigated to improve the power integrity of TSV-based 3D ICs. First, novel design topologies and analytic expressions are proposed for the physical implementation of *power gating* in 3D ICs. Power gating is an existing and effective low power design method to reduce leakage power consumption. It is demonstrated that the proposed methodology can effectively improve power integrity for 3D ICs with power gating. Alternatively, the efficacy of *decoupling capacitors*, which are intentional capacitors placed to reduce power supply noise, can be degraded due to power gating in 3D ICs. A reconfigurable decoupling capacitor topology that dynamically configures the connectivity of decoupling capacitors is investigated to achieve better utilization of the decoupling capacitors and further enhance power integrity of 3D ICs with power gating. In addition, to provide a fast yet accurate estimation of power supply noise, an analytic model and closed-form expressions are proposed, exhibiting significant improvement over existing analytical models for nanoscale ICs with fast transitions.

In addition to power integrity, TSV-based 3D ICs also introduce distinctive signal integrity issues. Electrical noise can couple from the TSVs into the silicon substrate of a die, which can disturb the operation of the active devices within the die. A methodology is developed to characterize the TSV induced noise coupling in 3D ICs. Design guidelines are also proposed based on the noise characterization results to improve signal integrity within 3D ICs.

Finally, the monolithic 3D integration technology based on MIVs (rather than TSVs) is investigated. To evaluate the benefits of MIV-based 3D ICs, *Mono3D*, a standard cell library for transistor-level monolithic 3D ICs, is developed in 45 nm CMOS technology. A complete back-end physical design flow utilizing the proposed *Mono3D* library is also demonstrated. As an example, a benchmark circuit is designed from gate-level netlist to physical layout using the *Mono3D* to evaluate the performance and power consumption of MIV-based 3D ICs.

# **Table of Contents**

| Al | bstrac  | et      | · · · · · · · · · · · · · · · · · · · | V |

|----|---------|---------|---------------------------------------|---|

| Li | st of I | Figures | X                                     | V |

| Li | st of ] | Fables  | xvi                                   | i |

| A  | cknow   | vledgen | ients xiz                             | X |

| 1  | Intr    | oductio | n                                     | 1 |

|    | 1.1     | Interco | onnect-Centric Design                 | 1 |

|    | 1.2     | Introd  | uction to 3D Integration              | 4 |

|    | 1.3     |         |                                       | 5 |

|    | 1.4     | Outlin  | e                                     | 8 |

| 2  | Pow     | er and  | Signal Integrity in 3D ICs 11         | 1 |

|    | 2.1     | 3D Int  | egration Technologies                 | 1 |

|    |         | 2.1.1   | TSV Structure and Parasitic Impedance | 5 |

|    |         |         | TSV Fabrication Technologies          | 6 |

|    |         | 2.1.3   | Progress in 3D Integrated Circuits    | 8 |

|    | 2.2     | Power   | Integrity                             | 0 |

|    |         | 2.2.1   | Power Supply Noise                    | 0 |

|    |         | 2.2.2   | Power Distribution Networks in 3D ICs | 2 |

|    |         | 2.2.3   | Decoupling Capacitance                | 7 |

|    | 2.3     | Signal  | Integrity                             | 9 |

|    |         | 2.3.1   | Crosstalk                             | 9 |

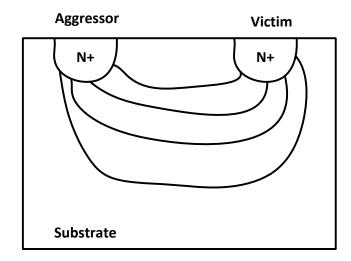

|    |         | 2.3.2   | Substrate Coupling                    | 0 |

|    |         | 2.3.3   | TSV-Induced Noise Coupling            | 1 |

| 3 | Pow  | er Gating in 3D Integrated Circuits                               | 33 |

|---|------|-------------------------------------------------------------------|----|

|   | 3.1  | Low Power IC Design Methodologies                                 | 33 |

|   | 3.2  | Power Gating                                                      | 36 |

|   |      | 3.2.1 Sleep Transistors and Power Distribution Network            | 37 |

|   | 3.3  | Proposed Power Gating Topologies for 3D ICs                       | 38 |

|   |      | 3.3.1 Lumped and Distributed Topologies                           | 39 |

|   |      | 3.3.2 Comparison Between Metal Via Stack and TSV Resistance .     | 41 |

|   | 3.4  | Simulation Results                                                | 42 |

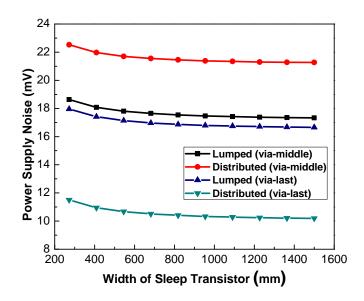

|   |      | 3.4.1 Power Supply Noise                                          | 44 |

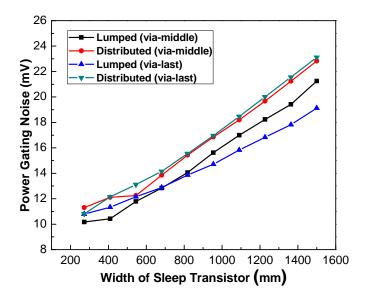

|   |      | 3.4.2 Power Gating Noise                                          | 45 |

|   |      | 3.4.3 Turn-on Time                                                | 47 |

|   |      | 3.4.4 Leakage Power Reduction                                     | 47 |

|   | 3.5  | Summary                                                           | 49 |

| 4 | Rese | ource Allocation Methodology for TSVs and Sleep Transistors in 3D |    |

|   |      | with Power Gating                                                 | 50 |

|   | 4.1  | Design Tradeoffs between TSVs and Sleep Transistors               | 51 |

|   | 4.2  | Proposed Methodology                                              | 52 |

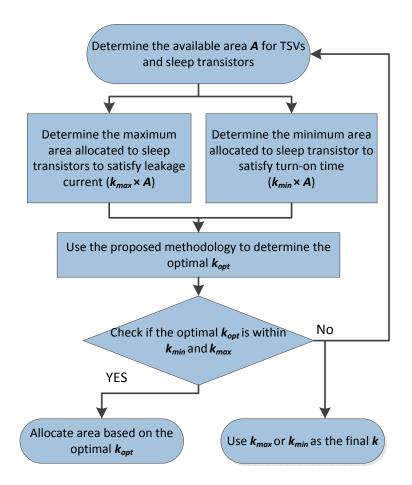

|   |      | 4.2.1 Summary of the Proposed Flow                                | 52 |

|   |      | 4.2.2 Proposed Analytic Expressions to Determine $k_{opt}$        | 54 |

|   |      | 4.2.3 Area Dependence                                             | 60 |

|   | 4.3  | Simulation Results                                                | 61 |

|   |      | 4.3.1 Simulation Setup                                            | 62 |

|   |      | 4.3.2 Verification of the Proposed Methodology                    | 66 |

|   | 4.4  | Summary                                                           | 69 |

| 5 | Clos | ed-Form Expressions to Estimate Power Supply Noise with Fast      |    |

|   |      | al Transitions                                                    | 70 |

|   | 5.1  | Previous Work in Power Supply Noise Modeling                      | 71 |

|   | 5.2  | Contributions of This Work                                        | 74 |

|   | 5.3  | Motivational Example on Peak Supply Noise and Damping Behavior    | 75 |

|   | 5.4  | Proposed Model for On-Chip Power Supply Noise                     | 79 |

|   |      | 5.4.1 Proposed Closed-Form Expressions for Power Supply Noise     | 79 |

|   |      | 5.4.2 Effect of Input Transition Time on Peak Power Supply Noise  | 83 |

|   | 5.5  | Simulation Results                                                | 87 |

|   |      | 5.5.1 Estimation of the Power Supply Noise Waveform               | 88 |

|   |      | 5.5.2 Estimation of the Peak Noise                                | 89 |

|   | 5.6  | Summary                                                           | 93 |

|   |      |                                                                   |    |

| 6 | Dec  | oupling Capacitor Topologies for TSV Based 3D ICs with Power       |    |

|---|------|--------------------------------------------------------------------|----|

|   | Gat  |                                                                    | )5 |

|   | 6.1  | Decoupling Capacitors in 3D ICs with Power Gating 9                | 96 |

|   | 6.2  | Decoupling Capacitor Topologies for Power-Gated 3D ICs 9           | 97 |

|   |      |                                                                    | 98 |

|   |      |                                                                    | 99 |

|   | 6.3  | Case Study                                                         | )1 |

|   |      | 6.3.1 Reconfigurable Switch and Decoupling Capacitor Sizing 10     | )1 |

|   |      | 6.3.2 Simulation Results                                           |    |

|   | 6.4  | Summary                                                            | .5 |

| 7 | Con  | npact Model to Efficiently Characterize TSV-to-Transistor Noise    |    |

|   | Cou  | ipling in 3D ICs 11                                                | 6  |

|   | 7.1  | $\mathcal{O}$ 1 $\mathcal{O}$                                      |    |

|   |      | 7.1.1 TSV Model                                                    | .8 |

|   |      | 7.1.2 Substrate Model                                              | 21 |

|   |      | 7.1.3 Accuracy and Limitations of the Distributed Model 12         | 22 |

|   | 7.2  | Compact Π Model For Efficient TSV Noise Coupling Analysis 12       | 23 |

|   |      | 7.2.1 Accuracy Analysis                                            | 25 |

|   |      | 7.2.2 Complexity Analysis                                          | 26 |

|   | 7.3  | TSV Safe Zone Characterization                                     | 27 |

|   | 7.4  | Design Guidelines                                                  | 32 |

|   |      | 7.4.1 Placement of Substrate Contacts                              | 32 |

|   |      | 7.4.2 Slew Rate of the TSV Signal                                  | 36 |

|   |      | 7.4.3 Voltage Swing of the TSV Signal                              | 38 |

|   |      | 7.4.4 Differential TSV Signaling                                   | 38 |

|   | 7.5  | Summary                                                            | 0  |

| 8 | Desi | ign and Characterization of a Standard Cell Library for Monolithic |    |

|   | 3D I | ICs 14                                                             | 1  |

|   | 8.1  |                                                                    |    |

|   |      | 8.1.1 Fabrication of MIV-based 3D ICs                              | 12 |

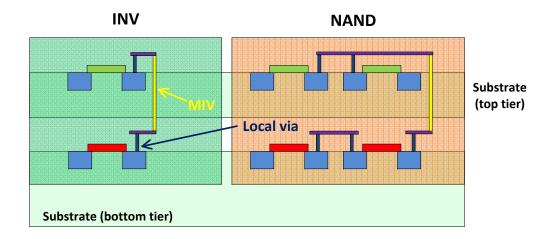

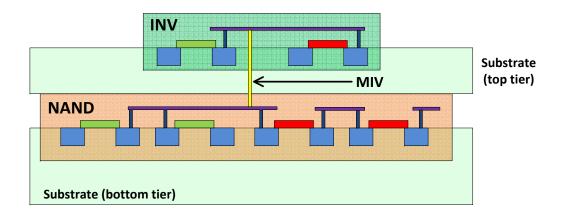

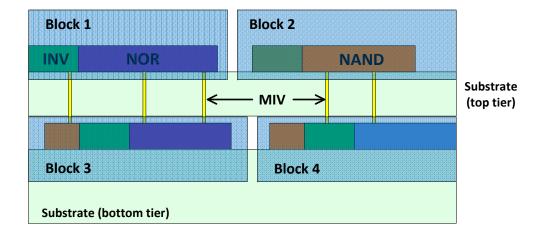

|   |      | 8.1.2 Different Design Styles in MIV-based 3D ICs                  | 4  |

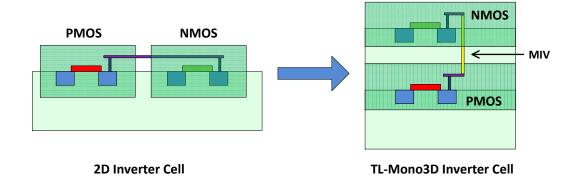

|   | 8.2  | Monolithic 3D Standard Cell Library                                | 6  |

|   |      | 8.2.1 Comparison of Mono3D cells and 2D Cells                      | 51 |

|   | 8.3  | Developing a Monolithic 3D IC with the Mono3D Standard Cell        |    |

|   |      | Library                                                            | 53 |

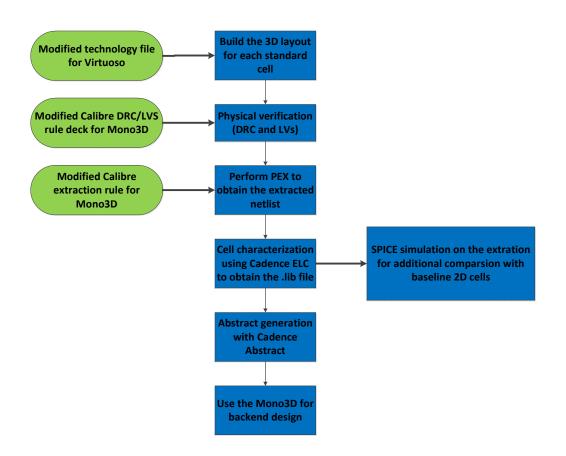

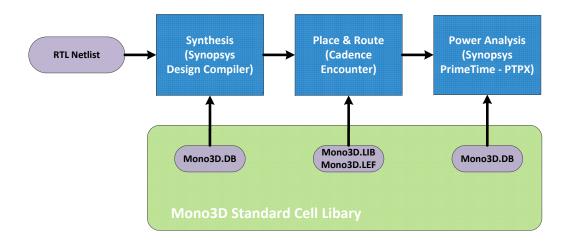

|   |      | 8.3.1 Physical Design Flow with the Mono3D Library 15              | 53 |

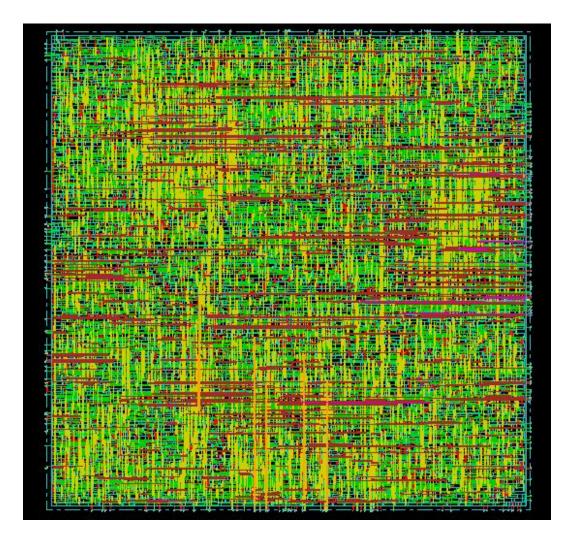

|    | 8.4              | 8.3.2 Monolithic 3D IC Design with the Mono3D Library Summary            |  |  |

|----|------------------|--------------------------------------------------------------------------|--|--|

| 9  | 9.1              | clusion and Future Work         Dissertation Summary         Future Work |  |  |

| Bi | Bibliography 162 |                                                                          |  |  |

# **List of Figures**

| Delay comparison caused by transistor, local interconnect, and global interconnect in sub-micron technology nodes | 3                                           |

|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------|

|                                                                                                                   |                                             |

| •                                                                                                                 |                                             |

| short and low resistive vertical connections in a 3D stack                                                        | 4                                           |

| Example of the vertical connections among multiple planes in System-                                              |                                             |

| in-Package 3D Integration: (a) wire bonds, and (b) solder balls                                                   | 12                                          |

| Inter-chip interconnects in different 3D integration technologies:                                                |                                             |

| (a) Wire bonding based SiP, (b) solder balls based SiP, and (c) TSV-                                              |                                             |

| based 3D IC                                                                                                       | 13                                          |

| Capacitively coupled 3D integration.                                                                              | 14                                          |

| Inductively coupled 3D integration.                                                                               | 14                                          |

| TSV characteristics: (a) cross-section of a TSV consisting of a con-                                              |                                             |

| ductive material and dielectric layer, (b) electrical model of a TSV                                              |                                             |

| illustrating the parasitic impedances                                                                             | 16                                          |

| Comparison of the connectivity schemes of via-first/middle TSVs                                                   |                                             |

| and via-last TSVs                                                                                                 | 18                                          |

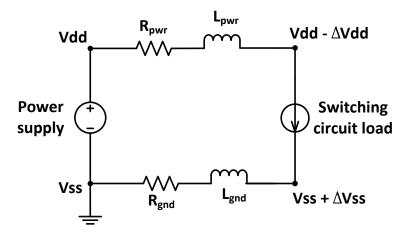

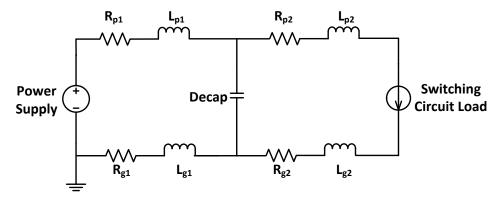

| Power noise caused by the parasitic impedances of the power deliv-                                                |                                             |

| ery path                                                                                                          | 21                                          |

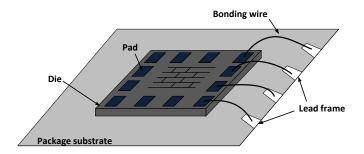

| Wire bonding method for package-to-die interface.                                                                 | 23                                          |

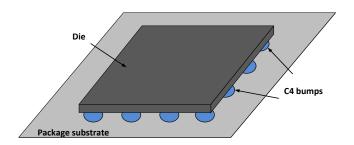

| Flip-chip method for package-to-die interface.                                                                    | 23                                          |

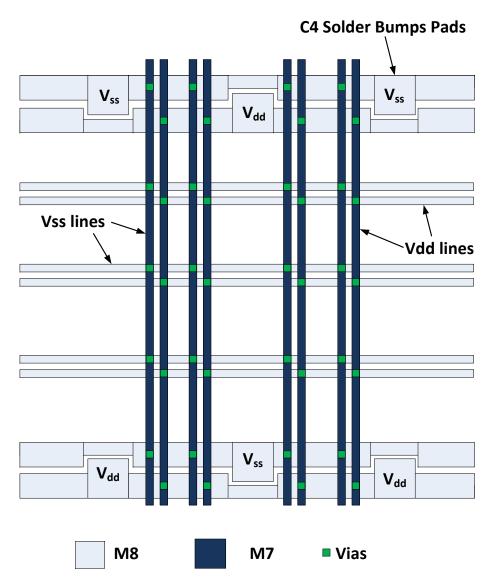

| Structure of a global power grid in a high performance micropro-                                                  |                                             |

| cessor                                                                                                            | 25                                          |

| Illustrative structure of a power distribution network of a three-                                                |                                             |

| plane 3D IC consisting of C4 bumps, global power grids, local                                                     |                                             |

| power grids, and TSVs                                                                                             | 27                                          |

| The circuit model of a power distribution network with decoupling                                                 |                                             |

| capacitor.                                                                                                        | 28                                          |

|                                                                                                                   | interconnect in sub-micron technology nodes |

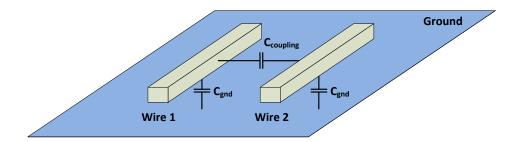

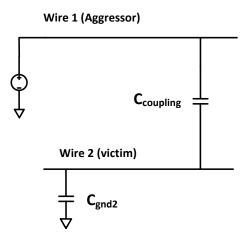

| 2.13 | Crosstalk between two adjacent wires.                                                                                                                                                                            | 29 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.14 | Electrical model for crosstalk analysis.                                                                                                                                                                         | 30 |

| 2.15 | Current flows within the substrate causing noise coupling between aggressor and victim.                                                                                                                          | 31 |

| 2.16 | Three-dimensional integration of diverse planes using TSV tech-<br>nology.                                                                                                                                       | 32 |

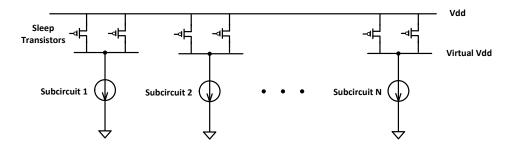

| 3.1  | Sleep transistors to control the power delivery of individual circuit blocks.                                                                                                                                    | 36 |

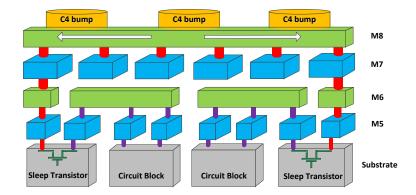

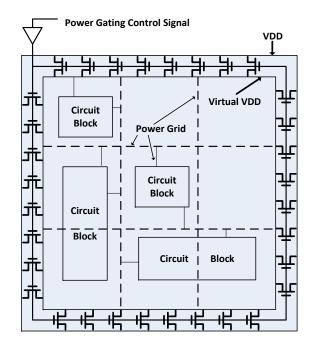

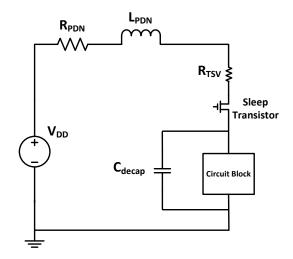

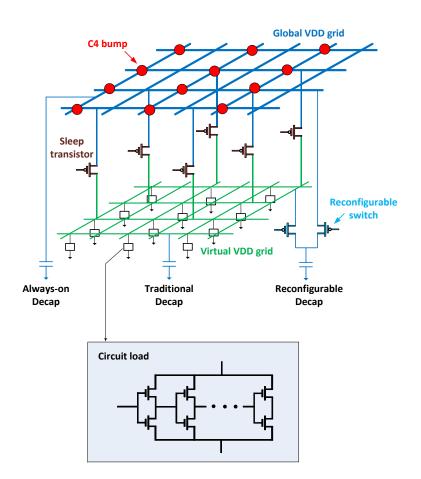

| 3.2  | Physical structure of a power distribution network with power gating.                                                                                                                                            | 38 |

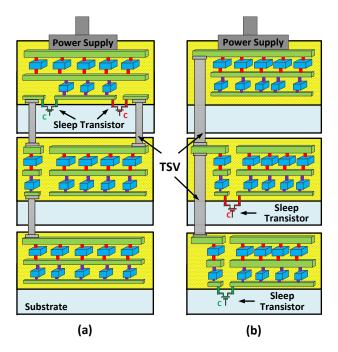

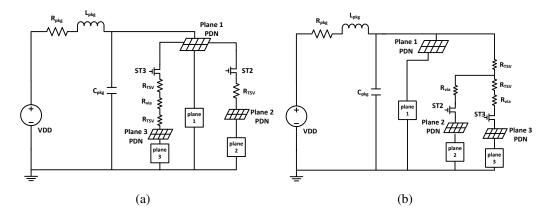

| 3.3  | Physical structures of proposed power gating topologies: (a) lumped                                                                                                                                              | 50 |

| 0.0  | power gating topology, and (b) distributed power gating topology.                                                                                                                                                | 39 |

| 3.4  | Simplified equivalent model of a three-plane power distribution net-<br>work consisting of: (a) via-middle TSVs with lumped power gating<br>topology, and (b) via-last TSVs with distributed power gating topol- |    |

|      | ogy                                                                                                                                                                                                              | 43 |

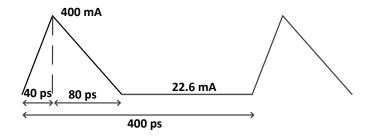

| 3.5  | Current waveform used to mimic switching current within an area                                                                                                                                                  |    |

|      | of $1 \text{ mm}^2$                                                                                                                                                                                              | 44 |

| 3.6  | Power supply noise produced by the proposed power gating topolo-<br>gies: (a) effect of the size of sleep transistor, and (b) effect of num-                                                                     |    |

|      | ber of TSVs.                                                                                                                                                                                                     | 45 |

| 3.7  | Power gating noise as a function of sleep transistor size for the pro-<br>posed power gating topologies.                                                                                                         | 46 |

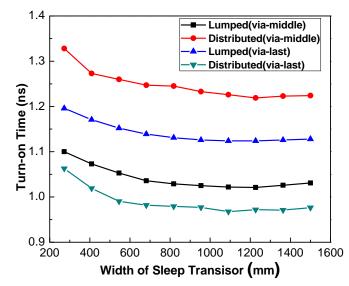

| 3.8  | Turn-on time of different power gating topologies with varying sleep                                                                                                                                             | 40 |

| 5.0  | transistor size.                                                                                                                                                                                                 | 48 |

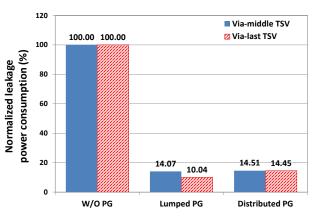

| 3.9  | Normalized leakage power consumption achieved the proposed power                                                                                                                                                 |    |

|      | gating topologies.                                                                                                                                                                                               | 48 |

| 4.1  | Ring style sleep transistor placement for coarse-grain power gating.                                                                                                                                             | 52 |

| 4.2  | Summary of the proposed resource allocation methodology                                                                                                                                                          | 53 |

| 4.3  | Simplified model of a power delivery path illustrating sleep transis-                                                                                                                                            | 56 |

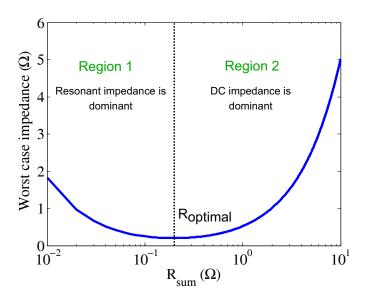

| 1 1  | tors and TSVs. $\dots$ tors impodence $Z$ warving with $R$                                                                                                                                                       | 56 |

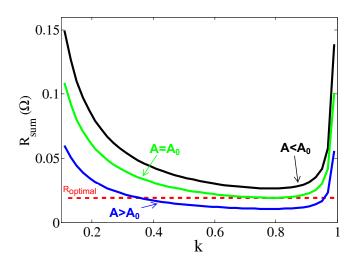

| 4.4  | The magnitude of worst case impedance $Z_{worst}$ varying with $R_{sum}$ values.                                                                                                                                 | 58 |

| 4.5  | The $R_{sum}$ under different k values with three area constraint A =                                                                                                                                            |    |

|      | 11000 $\mu m^2$ , A = 8000 $\mu m^2$ and A = 20000 $\mu m^2$                                                                                                                                                     | 60 |

|      |                                                                                                                                                                                                                  |    |

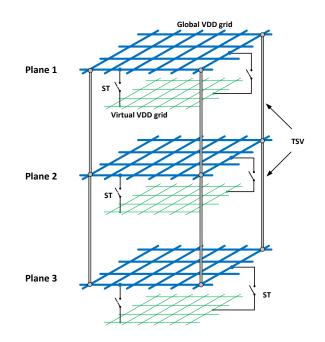

| 4.6  | Power distribution network of a three-plane 3D IC with via-last TSVs and power gating illustrating the global and virtual power                                                                                                     |   |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|

| 4.7  | grids, sleep transistors (ST), and TSVs                                                                                                                                                                                             | • | 62 |

| 4.7  | decoupling capacitors (traditional and proposed topologies), switch-<br>ing load circuits (gates with active devices), and the C4 bumps (for                                                                                        |   |    |

| 4.8  | the top plane only)                                                                                                                                                                                                                 | • | 63 |

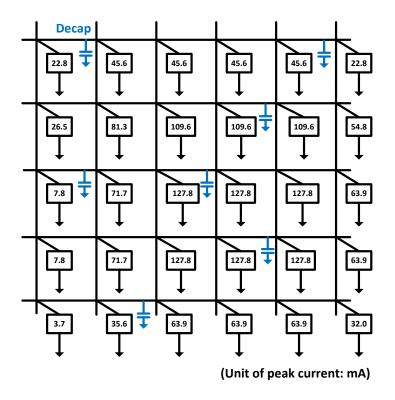

|      | power density reaches $40 \text{ W/cm}^2$ , which is comparable to the power density in modern processors.                                                                                                                          |   | 67 |

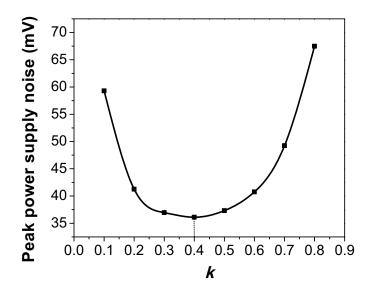

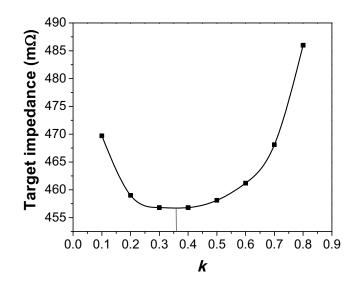

| 4.9  | Peak transient power supply noise of a circuit load in the bottom-                                                                                                                                                                  | • |    |

| 4.10 | most plane under different values of $k$                                                                                                                                                                                            | • | 68 |

| 4.10 | predicted from the proposed analytical model                                                                                                                                                                                        | • | 69 |

| 5.1  | Equivalent circuit typically used in existing work to develop closed-<br>form expressions for power supply noise.                                                                                                                   |   | 72 |

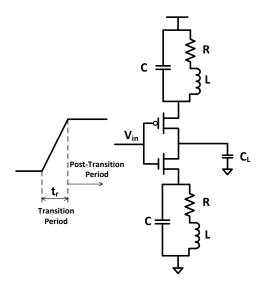

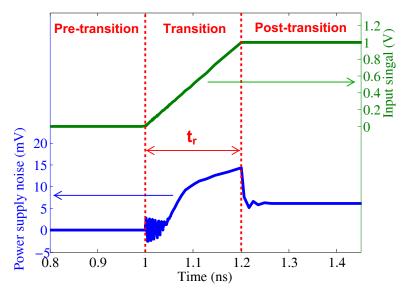

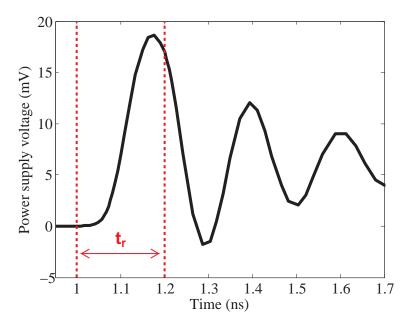

| 5.2  | Transient power supply noise waveform when parasitic capacitance<br>is ignored: R=5 $\Omega$ , L=1 nH, W <sub>n</sub> =1 $\mu$ m and W <sub>p</sub> =2 $\mu$ m, C <sub>L</sub> = 10 pF,<br>transition time t <sub>r</sub> is 200 ps |   | 76 |

| 5.3  | Transient power supply noise waveform when parasitic capacitance<br>is considered: R=5 $\Omega$ , L=1 nH, C=1 pF, W <sub>n</sub> =1 $\mu$ m and W <sub>p</sub> =2 $\mu$ m,                                                          | • | 70 |

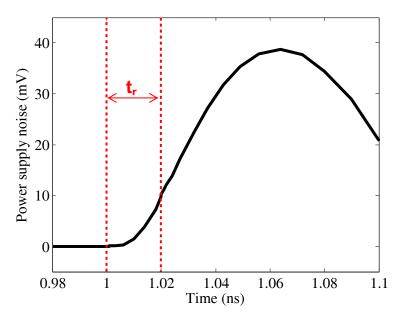

| 5.4  | $C_L = 10$ pF, transition time $t_r$ is 200 ps                                                                                                                                                                                      | • | 77 |

| 5.4  | of the input signal is reduced to 20 ps: R=5 $\Omega$ , L=1 nH, C=1 pF,<br>W <sub>n</sub> =1 $\mu$ m and W <sub>p</sub> =2 $\mu$ m, C <sub>L</sub> = 10 pF.                                                                         |   | 78 |

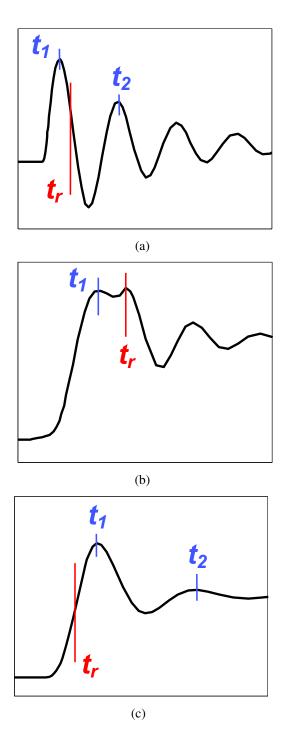

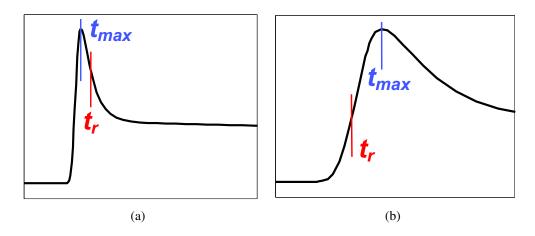

| 5.5  | Illustrative examples on the occurrence time of peak power supply<br>noise in underdamped case: (a) peak noise occurs within the tran-<br>sition period, (b) peak noise occurs at end of the transition period,                     |   |    |

|      | and (c) peak noise occurs within the post-transition period,                                                                                                                                                                        | • | 85 |

| 5.6  | Illustrative examples on the occurrence time of peak power supply<br>noise in overdamped case: (a) peak noise occurs within the tran-<br>sition period, and (b) peak noise occurs within the post-transition                        |   |    |

|      | period                                                                                                                                                                                                                              | • | 87 |

|      |                                                                                                                                                                                                                                     |   |    |

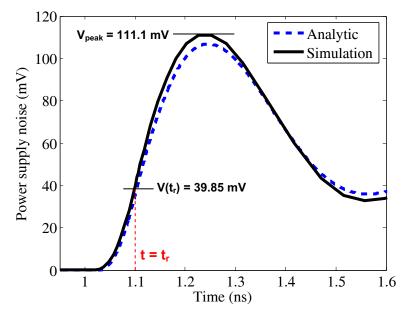

| 5.7 | Comparison of the power supply noise waveform in underdamped case as predicted by the proposed expressions and SPICE simulations. R=5 $\Omega$ , L=1 nH, C=10 pF, $t_r$ =100 ps, W <sub>n</sub> =100 nm, W <sub>p</sub> =200 nm, $C_L$ = 10 pF, and N=100.                                                                                     | . 88      |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

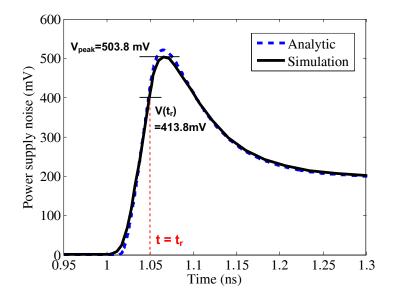

| 5.8 | Comparison of the power supply noise waveform in overdamped case as predicted by the proposed expressions and SPICE simulations. R=5 $\Omega$ , L=1 nH, C=1 pF, $t_r$ =50 ps, W <sub>n</sub> =100 nm, W <sub>p</sub> =200 nm, $C_L$ = 10 pF, and N=500.                                                                                        | . 89      |

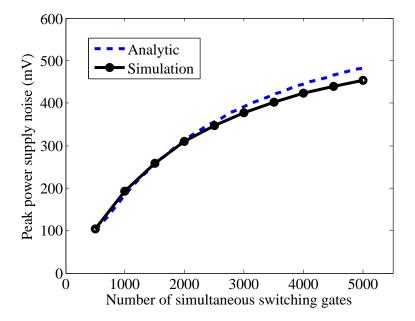

| 5.9 | Comparison of the peak power supply noise predicted by the proposed expressions and obtained by SPICE simulations as the number of simultaneously switching gates increases. R=0.5 $\Omega$ , L=100 pH, C=1 pF, $t_r$ =100 ps, W <sub>n</sub> =100 nm, W <sub>p</sub> =200 nm, $C_L$ = 10 pF                                                   |           |

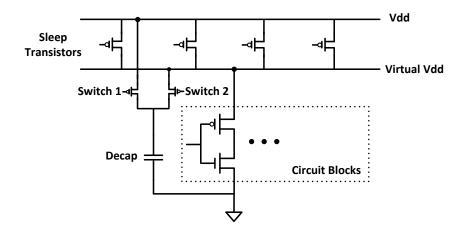

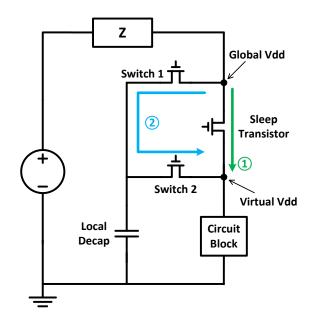

| 6.1 | Conceptual representation of the reconfigurable decoupling capac-<br>itor topology with power gating.                                                                                                                                                                                                                                          | . 98      |

| 6.2 | Illustration of the additional resistive path between the global and virtual power networks formed by the reconfigurable switches.                                                                                                                                                                                                             | . 90      |

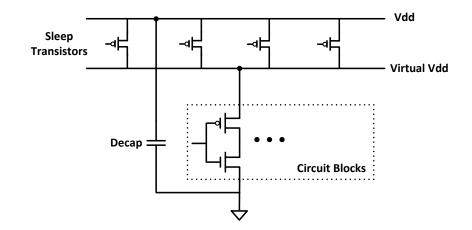

| 6.3 | Conceptual representation of the always-on decoupling capacitor topology with power gating.                                                                                                                                                                                                                                                    | . 100     |

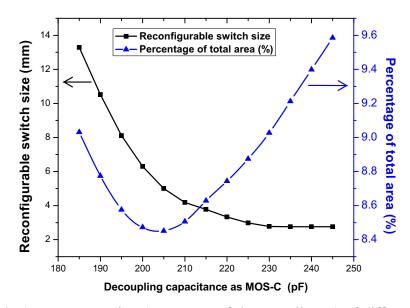

| 6.4 | Area consumption (as percent of the overall area) of different pairs<br>of decoupling capacitance and reconfigurable switch size. Note that<br>each pair satisfies the power supply noise constraint of 50 mV (5%<br>of the supply voltage). Area overhead is minimized at a specific<br>pair. Decoupling capacitors are implemented as MOS-C. |           |

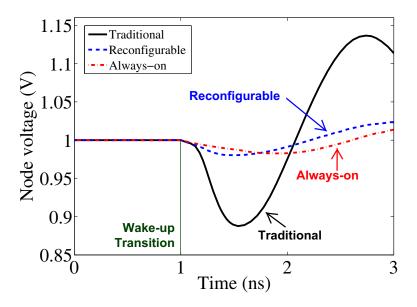

| 6.5 | Transient behavior of the on-voltage at a specific node within virtual grid of the bottom plane for each topology for scenario 3 (first two                                                                                                                                                                                                    |           |

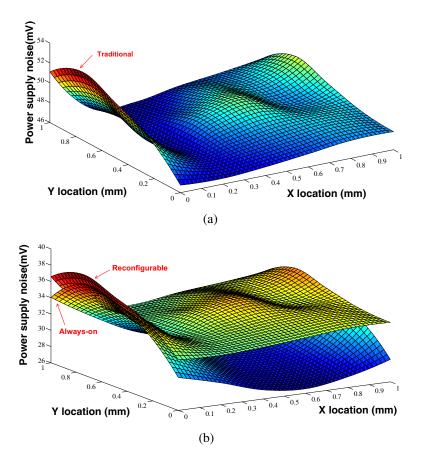

| 6.6 | planes are power gated and the bottom plane is active) Spatial distribution of the peak power supply noise on the bottom plane for scenario 3 (first two planes are power gated and the bottom plane is active): (a) traditional topology, (b) reconfigurable and always-on topologies                                                         |           |

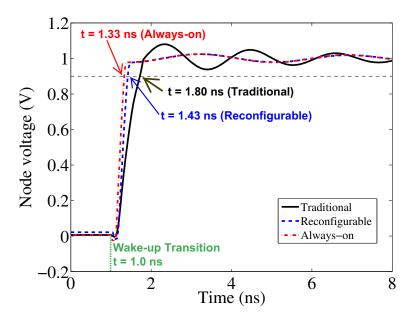

| 6.7 | Transient behavior of power gating noise at a specific node within<br>the bottom plane for each topology for scenario 3 (top plane is<br>power gated and middle plane transitions from off to on state at                                                                                                                                      | . 111     |

| 6.8 | 1 ns)                                                                                                                                                                                                                                                                                                                                          |           |

|     |                                                                                                                                                                                                                                                                                                                                                | • • • • • |

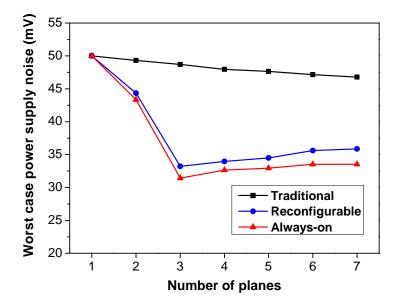

| 6.9 | Peak power supply noise on the top plane as the number of power gated planes increases                                                                    |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

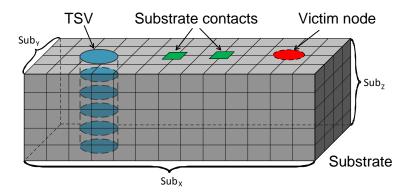

| 7.1 | Physical structure used to analyze TSV induced noise coupling 117                                                                                         |

| 7.2 | TSV representations: (a) cross-section of a TSV consisting of a conductive material and dielectric layer, (b) electrical model of a                       |

|     | unit TSV cell used for discretization.                                                                                                                    |

| 7.3 | Distributed model of a substrate network where each unit cell is                                                                                          |

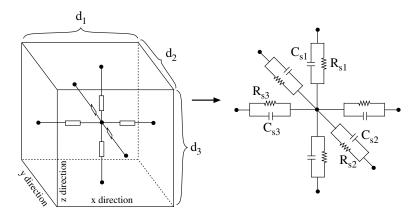

| 1.0 | represented by six resistances and capacitances                                                                                                           |

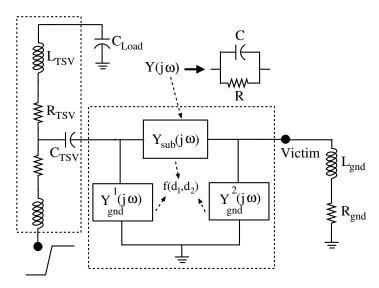

| 7.4 | Compact $\pi$ model to efficiently estimate the noise at the victim node                                                                                  |

| ,   | in the presence of a TSV and substrate contacts                                                                                                           |

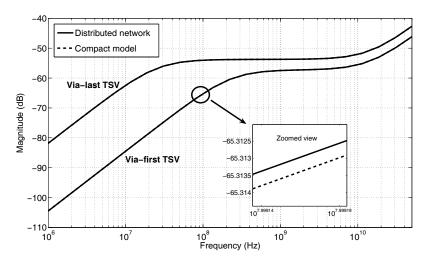

| 7.5 | Comparison of the proposed compact $\pi$ model with high complex-                                                                                         |

|     | ity distributed mesh for both via-first and via-last TSVs. The solid                                                                                      |

|     | line represents noise at the victim node obtained from distributed                                                                                        |

|     | mesh whereas the dashed line represents noise at the victim node                                                                                          |

|     | obtained from the compact $\pi$ model                                                                                                                     |

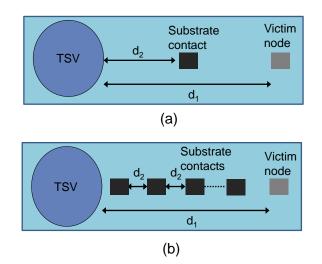

| 7.6 | Two substrate biasing schemes used to characterize noise coupling:                                                                                        |

|     | (a) single substrate contact between TSV and victim node, (b) reg-                                                                                        |

|     | ular placement of the substrate contacts between TSV and victim                                                                                           |

|     | node                                                                                                                                                      |

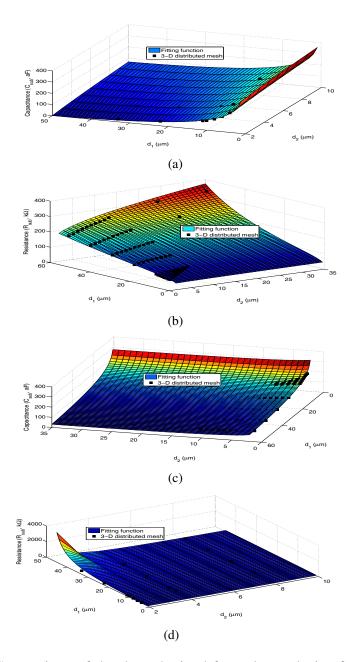

| 7.7 | Comparison of the data obtained from the analysis of the distributed                                                                                      |

|     | mesh with the function $F$ that approximates these data: (a) resis-                                                                                       |

|     | tance $R_{sub}$ of the $Y_{sub}(j\omega)$ with a via-first TSV and a single sub-                                                                          |

|     | strate contact (case 1), (b) capacitance $C_{sub}$ of the $Y_{sub}(j\omega)$ with a via-first TSV and a single substrate contact (case 1), (c) resistance |

|     | $R_{sub}$ of the $Y_{sub}(j\omega)$ with a via-last TSV and regularly placed sub-                                                                         |

|     | strate contacts (case 4), and (d) capacitance $C_{sub}$ of the $Y_{sub}(j\omega)$                                                                         |

| 7.8 | with a via-last TSV and regularly placed substrate contacts (case 4). 130                                                                                 |

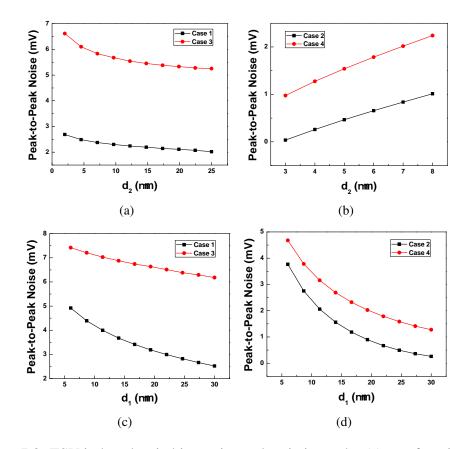

| 1.0 | TSV induced switching noise at the victim node: (a) as a function of $d_2$ at constant $d_1$ for case 1 and case 3, (b) as a function of $d_2$ at         |

|     | constant $d_1$ for case 2 and case 4, (c) as a function of $d_1$ at constant                                                                              |

|     | $d_2$ for case 1 and case 3, and (d) as a function of $d_1$ at constant $d_2$                                                                             |

|     | for case 2 and case 4. $\dots$ 133                                                                                                                        |

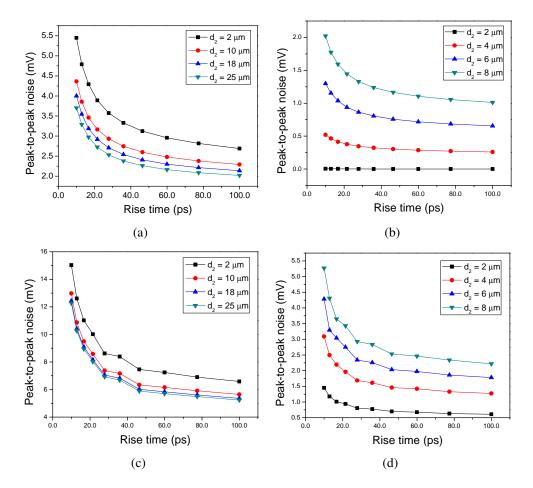

| 7.9 | TSV induced switching noise at the victim node as a function of                                                                                           |

| 1.) | rise time: (a) case 1: via-first TSV with a single substrate contact,                                                                                     |

|     | (b) case 2: via-first TSV with regularly placed substrate contacts,                                                                                       |

|     | (c) case 3: via-last TSV with a single substrate contact, and (d) case                                                                                    |

|     | 4: via-last TSV with regularly placed substrate contacts                                                                                                  |

|     |                                                                                                                                                           |

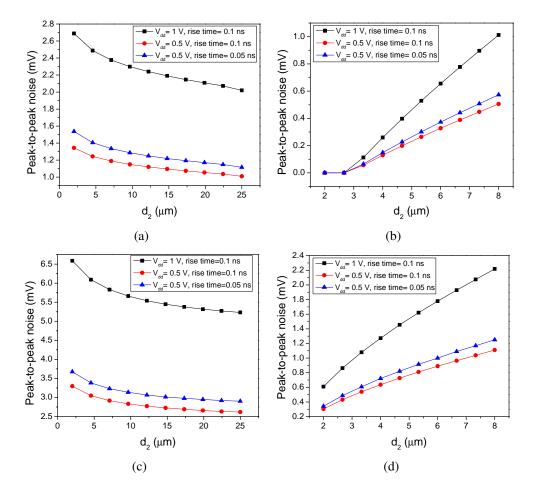

| 7.10 | TSV induced switching noise at the victim node at different volt-<br>age swings and rise times : (a) case 1: via-first TSV with a single<br>substrate contact, (b) case 2: via-first TSV with regularly placed<br>substrate contacts, (c) case 3: via-last TSV with a single substrate<br>contact, and (d) case 4: via-last TSV with regularly placed substrate |     |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | contacts                                                                                                                                                                                                                                                                                                                                                        | 137 |

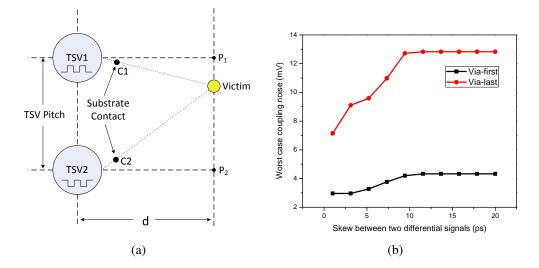

| 7.11 | Effect of differential signaling on TSV related noise coupling, (a) analysis setup and (b) noise at the victim node as a function skew                                                                                                                                                                                                                          |     |

|      | between the two signals.                                                                                                                                                                                                                                                                                                                                        | 139 |

| 0.1  | Manalishia 2D integration with MIVs on the integration vertical con                                                                                                                                                                                                                                                                                             |     |

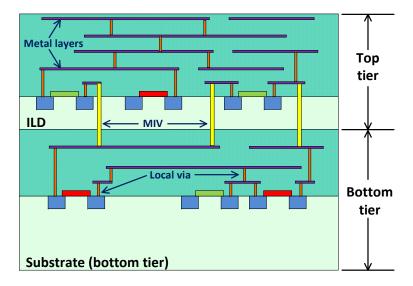

| 8.1  | Monolithic 3D integration with MIVs as the inter-tier vertical con-<br>nections.                                                                                                                                                                                                                                                                                | 142 |

| 8.2  | Transistor-level monolithic 3D integration design style, where all                                                                                                                                                                                                                                                                                              | 142 |

| 0.2  | of the PMOS transistors are fabricated on one tier and all of the                                                                                                                                                                                                                                                                                               |     |

|      | NMOS transistors are fabricated on the other tier.                                                                                                                                                                                                                                                                                                              | 145 |

| 8.3  | Gate-level monolithic 3D integration design style.                                                                                                                                                                                                                                                                                                              |     |

| 8.4  | Block-level monolithic 3D integration design style.                                                                                                                                                                                                                                                                                                             |     |

| 8.5  | Process of building the standard cell library.                                                                                                                                                                                                                                                                                                                  |     |

| 8.6  | Comparison of the physical structure of an inverter standard cell in                                                                                                                                                                                                                                                                                            | 110 |

| 0.0  | traditional 2D and TL-Mono 3D.                                                                                                                                                                                                                                                                                                                                  | 149 |

| 8.7  | Physical design flow utilizing the Mono3D standard cell library.                                                                                                                                                                                                                                                                                                |     |

| 8.8  | Layout of a benchmark circuit designed with the Mono3D standard                                                                                                                                                                                                                                                                                                 | 100 |

|      | cell library.                                                                                                                                                                                                                                                                                                                                                   | 155 |

# **List of Tables**

| 3.1<br>3.2<br>3.3<br>3.4 | Physical characteristics of vias in a 45 nm technology.Physical characteristics of TSVs.Physical characteristics of the global power grid.Physical characteristics of the sleep transistors. | 41<br>42<br>43<br>44 |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 4.1                      | Primary physical characteristics of the global and virtual power grids.                                                                                                                      | 64                   |

| 4.2                      | Parasitic impedances of the unit interconnect segment within the global and virtual power grids.                                                                                             | 64                   |

| 4.3                      | Package, TSV, and C4 bump parasitic impedances and physical characteristics.                                                                                                                 | 65                   |

| 5.1                      | Boundary conditions on damping characteristics as obtained from                                                                                                                              | 0.0                  |

| 5.2                      | (5.8)                                                                                                                                                                                        | 83                   |

| 5.3                      | ps                                                                                                                                                                                           | 90                   |

|                          | for a variety of <i>RLC</i> parasitic impedances when N=100 and $t_r$ =50 ps.                                                                                                                | 91                   |

| 6.1                      | Size of the decoupling capacitors and reconfigurable switches                                                                                                                                | 04                   |

| 6.2                      | Comparison of the physical area overhead of the traditional, recon-<br>figurable, and always-on topologies.                                                                                  | 04                   |

| 6.3                      | Power gating status of each plane in different scenarios. The paren-<br>theses indicate one plane is in transition from off state to on state                                                |                      |

|                          | for the measurement of power gating noise.                                                                                                                                                   | 06                   |

| 6.4                      | Peak power supply noise obtained from each scenario and noise re-<br>duction achieved by the proposed topologies (All of the decoupling                                                      |                      |

|                          | capacitors are implemented as MOS capacitors)                                                                                                                                                | 06                   |

| 6.5 | RMS power supply noise obtained from each scenario and noise re-       |

|-----|------------------------------------------------------------------------|

|     | duction achieved by the proposed topologies (All of the decoupling     |

|     | capacitors are implemented as MOS capacitors)                          |

| 6.6 | Peak power gating noise obtained from each scenario and noise re-      |

|     | duction achieved by the proposed topologies (All of the decoupling     |

|     | capacitors are implemented as MOS capacitors)                          |

| 6.7 | RMS power gating noise obtained from each scenario and noise re-       |

|     | duction achieved by the proposed topologies (All of the decoupling     |

|     | capacitors are implemented as MOS capacitors)                          |

| 6.8 | Overall Average Power Consumption (when all decoupling capaci-         |

|     | tors are implemented as MOS capacitors)                                |

| 7.1 | Fitting coefficients for the function $F$ that approximates the admit- |

|     | tances within the compact model (see Fig. 7.4) for each case. The      |

|     | function $F$ is given by (7.15)                                        |

| 8.1 | Standard cells available in the Mono3D library                         |

| 8.2 | Performance comparison of each individual standard cell in Mono3D      |

|     | and baseline 2D PDK                                                    |

| 8.3 | Performance comparison of the Mono3D based monolithic 3D cir-          |

|     | cuit and the 2D counterpart                                            |

|     |                                                                        |

### ACKNOWLEDGEMENTS

The past five years of my PhD experience is absolutely the most enjoyable five years in my life so far. There are these amazing people I would like to acknowledge here, who made pursuing PhD such a memorable journey.

First of all, I would like to pay my highest regards to my PhD advisor, Prof. Emre Salman. He is not only an academic advisor, but also a role model for me. Benefiting a lot from his academic perspective and professional knowledge, I also enjoyed the research environment he provided so I can focus on most interesting problems and make good progress in the area of 3D IC designs. From the numerous talks and discussions with Prof. Salman, I am so impressed that he can always quickly grasp the core points from a seemingly complicated problem and root-cause the issue. What I learned from Prof. Salman would for sure be a good fortune for me ever after.

I greatly appreciate the help from Prof. Sangjin Hong, Prof. Milutin Stanacevic and Prof. Thomas MacCarthy, especially for serving as my committee members and providing insightful advice to my dissertation.

I would also like to acknowledge all the members of NanoCAS Laboratory: Peirong, Zhihua, Suhas, Ziqi, Sateja, Mallika, Weicheng, Chen, Tutu, Yongwan... We shared so many good memories in our nice and comforting lab – our "home away from home". Thank you for making our academic adventure not only about experiments and circuit simulations, but also about friendship and trust. I wish you all have a fruitful research experience and a bright future. Last, but not least, I feel so grateful for the love from my parents Bibo Wang, Lin Wang, and my fiancee Xi. I would not never accomplish this without the unconditional support from you.

# Chapter 1

## Introduction

In the past several decades, integrated circuit (IC) design process has shifted from a logic-centric methodology to an interconnect-centric approach. This shift is described in Section 1.1. Three-dimensional (3D) integration, an enabling technology in the interconnect-centric design era, is introduced in Section 1.2. Challenges related with 3D integration technology are discussed in Section 1.3. The outline of this dissertation is presented in Section 1.4.

## **1.1 Interconnect-Centric Design**

The evolution of integrated circuit (IC) technology consists of interlaced limitations and breakthroughs to overcome these limitations. Since the development of the first IC in 1958, the primary objective has been cramming more transistors onto a single chip to achieve increasingly more complex functionality and better performance. The advances in semiconductor fabrication technology have enabled higher transistor density by scaling down the size of transistors. As Gordon Moore noted in 1965, the number of transistors on a single IC has doubled every 18 to 24 months [1]. This prediction has worked well for more than three decades. The number of transistors has increased from 2300 in the Intel 4004 processor released in 1971, by over 600 times, to 1.4 million in the Intel 486 processor released in 1992 [2].

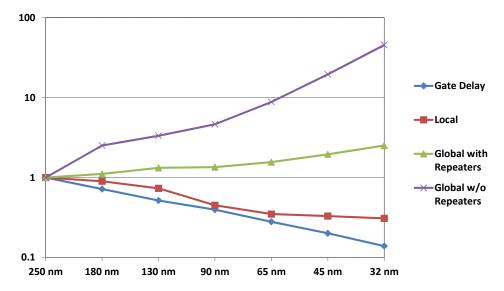

However, limitations have emerged as fabrication technology has entered the sub-micron era, where over one million transistors can be integrated onto a single chip. The interconnects required to connect a large number of transistors have raised a challenge to the ongoing trend of performance improvement enabled by device scaling [3] [4]. Previously, in the micron technology era where the transistor minimum feature size is above 1  $\mu$ m, the speed of transistor used to be the dominant factor for system performance. However, as the features size has decreased, the gate delay caused by transistors has been significantly reduced while the delay caused by interconnect has increased. As reported by the 2005 International Technology Roadmap for Semiconductors (ITRS) [5], at 0.25  $\mu$ m technology node, the interconnect delay is approximately equal to the gate delay caused by transistors, as shown in Fig. 1.1. Beyond this technology node, interconnect delay (particularly the delay caused by the long global interconnects) becomes dominant over transistor delay. Therefore, long global interconnects have become a bottleneck for the overall system performance [4].

Various methods have been proposed to address the interconnect issue. Migrating from aluminum to copper as the interconnect material is an early example of this effort. By using copper interconnects, resistivity of the metal interconnects is reduced, partially compensating the delay caused by long global interconnects [6]. Another technology-level innovation is the application of ultra-low *K* dielectric ma-

Figure 1.1: Delay comparison caused by transistor, local interconnect, and global interconnect in sub-micron technology nodes [5].

terials, which aims to address the parasitic capacitance of interconnects [7]. The high density of interconnect makes the lateral parasitic capacitance between neighboring metal lines an important issue, since the parasitic capacitance not only increases the signal delay but also causes additional power consumption [8]. The parasitic capacitance between adjacent metal lines is proportional to the dielectric constant K of the insulation material between the metal lines. Thus, low K dielectric materials such as carbon doped silicon and porous dielectric film are preferred over traditional silicon dioxide as the insulation material between interconnects [8].

The application of new materials brings a one-time reduction to the parasitic impedance of the interconnects. However, the limitations of long global interconnects subsequently emerge again as the scaling continues. Global interconnects with high resistance are required to connect different circuit modules within the die, which has become increasingly larger [9]. For example, the die size for Intel's

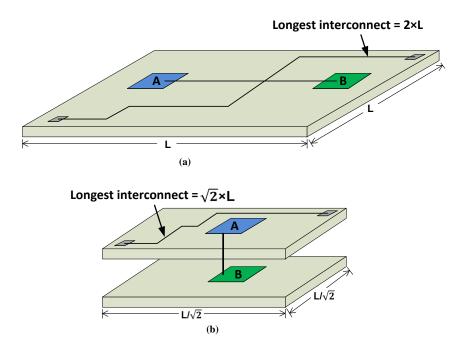

Figure 1.2: The communication between two blocks A and B is achieved by (a) long and high resistive global interconnect in 2D planar die, and (b) short and low resistive vertical connections in a 3D stack.

Haswell processors can be as high as 356 mm<sup>2</sup> [10]. Therefore, an intuitive solution is, instead of distributing the circuit modules in a 2D planar plane, the modules can be stacked vertically, *i.e.*, three-dimensional (3D) integration.

### **1.2 Introduction to 3D Integration**

In 3D integration technology, multiple dies (also referred to as tiers) are bonded and vertically stacked on top of each other. The communication between multiple tiers in the stack is achieved by vertical connections such as wire bonds, soldering balls, through-silicon-vias (TSVs) or monolithic inter-tier vias (MIVs) depending on the specific 3D integration technology. These vertical connections have smaller resistance than the global planar interconnects. Therefore, as shown in Fig. 1.2, two circuit blocks A and B, which experience longer interconnect in 2D planar die, can be closer in the vertical dimension utilizing 3D integration technology. The communication between these two blocks can be achieved by short and relatively low resistance vertical connections in the 3D system, instead of the long and highly resistive interconnects in the 2D counterpart. According to simple estimations, the longest interconnect length exhibits a reduction approximately proportional to  $\sqrt{N}$  when the 2D chip is converted into an *N*-plane 3D IC [9] [11]. The reduction in interconnect length not only reduces delay, but also power consumption due to less switching capacitance [12] [9].

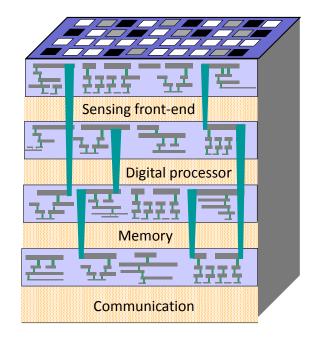

In addition to achieving shorter interconnects, 3D integration enables heterogenous integration of multiple dies with different functionalities and possibly fabricated using different technologies, such as analog senors, digital logic, memory, radio frequency (RF) components or micro-electro-mechanical system (MEMS) modules [13]. Due to these advantages, 3D integration has been considered as an enabling technology to maintain performance improvement in the interconnectcentric design era of ICs.

### **1.3 Challenges in 3D Integrated Circuits**

The advantages of 3D integration technology are highly desirable in future technology nodes to maintain higher integration densities while enhancing performance and reducing power. However, designing and fabricating 3D ICs have several important challenges, as outlined below.

In the past years, considerable research has been conducted on 3D integration

at the fabrication level. A fundamental issue in 3D IC fabrication is to reliably manufacture the vertical connections among the multiple dies within a 3D stack. Various 3D integration technologies have been developed, with different structures and mechanisms for the vertical connections, such as through-silicon-vias (TSV) and monolithic inter-tier vias (MIVs). For instance, in TSV based 3D ICs, vertical TSVs travel through the substrate of each tier to achieve interconnections. The reliability of these vertical connections is a concern which affects the overall reliability of the 3D IC. Alternatively, to bond multiple dies, specialized bonding techniques and wafer thinning processes are required [14] [15] [16].

With the continuous progress in fabrication technologies for 3D integration, the primary obstacles in realizing complex 3D ICs now lie in multiple aspects of the design process [9]. For example, when designing a complex system such as a microprocessor, the architecture level considerations need to be tailored to effectively exploit the advantages of 3D technology. Different circuit modules in the microprocessor should be optimally partitioned and placed on different planes in the 3D stack to achieve optimal performance for the entire system. Another imminent issue is the insufficiency of existing electronic design automation (EDA) tools for 3D ICs. For modern VLSI circuits with several billion transistors, EDA tools are critical components in the design process. New tools need to be developed to accommodate the novel characteristics achieved by the vertical connections in 3D ICs.

During the testing phase, 3D ICs exhibit unique characteristics requiring novel testing methodologies. Traditionally, testing is performed at wafer level and die level. Therefore, only one plane of a 3D IC can be tested at a time, which means only part of the system functionality is tested. Thus, additional connection pads and pins are required to provide input pattern as well as power and clock signals to the

tier under test [9] [17]. Alternatively, traditional testing methodologies of individual dies before bonding cannot guarantee the functionality of the overall 3D system. In 3D ICs, post-bonding testing methodologies which test the overall functionality of the system after bonding multiple dies are required [18] [19].

Another critical challenge in the physical design of 3D ICs is the power and signal integrity issues, which are the foci of this dissertation. To guarantee normal operation of a chip, power supply voltage should be reliably delivered to each transistor in the system without excessive power noise along the power delivery path, *i.e.*, maintaining system-wide power integrity [20]. Reliable delivery of the power supply voltage to every circuit module in a 3D IC is more challenging than a traditional 2D chip. The power distribution network on each die of a 3D stack is interconnected by the vertical connections (such as TSVs), generating a more complicated network. Higher parasitic impedance of this more complicated power distribution network exacerbates the power noise along the power delivery path. Furthermore, due to the heterogenous integration, certain low power design techniques such as power gating are often implemented, which further complicates the power distribution network due to the individual control of different power domains in the system. Therefore, novel design methodologies considering the unique characteristics of 3D ICs are developed in this dissertation to address power integrity issues.

Various forms of noise exist in an IC, which affect the operation of transistors and may cause functional failure. This issue is referred to as signal integrity. In addition to the traditional signal integrity issues encountered in 2D ICs (such as interconnect noise coupling [21] and substrate coupling [22]), 3D ICs experience new signal integrity challenges. For instance, in TSV-based 3D ICs, the TSVs inject noise into silicon substrate. This noise propagates and affects the active devices throughout the substrate. Therefore, accurate characterization of the noise coupling mechanisms and developing design guidelines for 3D ICs are essential to improve signal integrity, as targeted in this dissertation.

## 1.4 Outline

In this dissertation, research results about several critical issues related with power and signal integrity in 3D ICs are presented [23–28]. In Chapter 2, an overview of 3D ICs is provided. Power and signal integrity issues in 3D ICs are introduced to motivate the research described in this dissertation.

In Chapter 3, research results on implementing power gating in TSV-based 3D ICs are presented. Power gating is a well known low power design method to reduce leakage power consumption. Power gating requires additional transistors (referred to as sleep transistors) inserted along the power delivery path to realize individual control of the power delivery to each circuit module. In 3D ICs, the physical implementation of power gating is affected by the TSVs. In this chapter, several TSV-specific power gating schemes are proposed based on the characteristics of different TSV technologies to enhance power integrity.

In Chapter 4, a resource allocation methodology is proposed to simultaneously determine the size of sleep transistors and TSVs. The power supply noise is reduced with minimal area and power consumption overhead. The proposed methodology is important since both sleep transistors and TSVs occupy significant silicon area in 3D ICs.

In Chapter 5, the primary focus is on providing a fast yet accurate estimation

of the power supply noise, a practical issue encountered during power integrity analysis. It is demonstrated that existing closed-form expressions have a common limitation in analyzing power supply noise with fast signal transitions. Since modern technologies exhibit signal transitions in the range of tens of pico seconds, it is highly critical to be able to consider this characteristic. Thus, an analytical model with closed-form expressions is developed to accurately estimate power supply noise. The proposed expressions exhibit significant improvement in accuracy over existing analytical models, particularly for nanoscale ICs with fast signal transitions.

In Chapter 6, design considerations about decoupling capacitors in 3D ICs are explored. Placing decoupling capacitors is a well known method to reduce power supply noise. However, the placement topology of decoupling capacitors should be carefully determined to guarantee the efficacy of decoupling capacitors. In 3D ICs, the vertical TSVs extend the effective range of decoupling capacitors from a single plane to multiple planes within a 3D stack. However, if conventional power gating is applied, the ability of decoupling capacitors to reduce noise in neighboring planes cannot be exploited. Therefore, two decoupling capacitor placement topologies are proposed to utilize the low resistance of TSVs. With the proposed topologies, the decoupling capacitor in a power gated plane is enabled to mitigate power noise of the neighboring active planes, improving the overall power integrity of a 3D IC.

In Chapter 7, TSV-induced noise coupling in 3D ICs is investigated as an important signal integrity issue. A methodology is proposed to effectively characterize the noise coupling for different TSV types and substrate schemes. The effect of different design parameters such as TSV type, placement of substrate contacts, signal slew rate, and voltage swing is investigated. Design guidelines are developed to improve system-wide signal integrity.

In Chapter 8, a relatively more recent type of 3D integration; monolithic 3D approach with inter-tier vias (MIVs), is explored. MIVs achieve significantly higher density as compared to TSVs. Thus, monolithic 3D technology is considered to be a highly promising option for vertical integration. The *Mono3D*, a standard cell library for transistor-level monolithic 3D ICs, is developed by using a 45 nm technology kit. It is demonstrated that the proposed Mono3D standard cell library can be integrated with existing standard physical design flows. An example 3D monolithic IC with two planes is designed and analyzed by utilizing the developed cell library and physical design flow. The advantages of the monolithic 3D approach in terms of physical area and power consumption are characterized.

Finally, the dissertation is concluded in Chapter 9. Possible future research directions are discussed.

## Chapter 2

## **Power and Signal Integrity in 3D ICs**

To investigate the power and signal integrity issues in 3D ICs, the unique characteristics of 3D ICs should be explored, which are the foci of this chapter. Several 3D integration technologies are introduced in Section 2.1 with emphasis on TSV-based 3D ICs. A brief overview of the power noise issue and power distribution network in 3D ICs is provided in Section 2.2. Several critical noise coupling mechanisms affecting the system signal integrity are discussed in Section 2.3.

## 2.1 3D Integration Technologies

Currently, there are several 3D integration technologies available including Systemin-Package (SiP), TSV-based 3D integration, MIV-based 3D integration, and contactless coupled 3D ICs. A critical characteristic that distinguishes different 3D integration technologies is the vertical connectivity of different planes in a 3D stack.

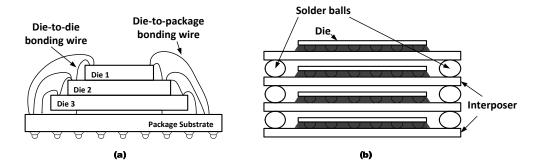

In System-in-Package (SiP) technology, multiple pre-fabricated dies are encapsulated within the same package. Within the package, connections among multi-

Figure 2.1: Example of the vertical connections among multiple planes in Systemin-Package 3D Integration: (a) wire bonds, and (b) solder balls.

ple stacked dies are implemented using methods such as wire bonding or solder balls [29]. For example, as shown in Fig. 2.1(a), wire bonds are placed around the perimeter of each die to achieve die-to-die connections, as well as die-to-package connections. Similarly, in solder ball based method, an additional layer called interposer is inserted between two adjacent dies in the stack, as shown in Fig. 2.1(b). Solder balls are placed around the peripheral of the interposer layer to achieve connections between two interposers, while the interposer layer provides the connection between solder balls and the die. Compared with the wire bonding method, more dies can be stacked using solder ball based method due to the reduced parasitic impedance of solder balls [29].

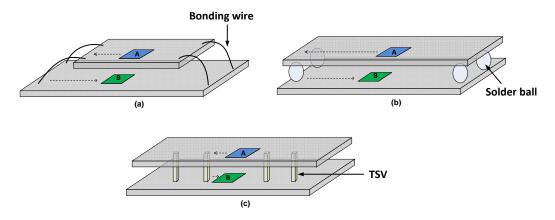

However, although SiP reduces the off-chip interconnect length, the peripheral locations of bonding wires or solder balls undermine the advantage of reducing inter-plane interconnect length of 3D integration. As illustrated in Fig 2.2 (a) and (b), for two circuit blocks A and B which are located on different planes in a 3D stack, if wire bonds or solder balls are used to connect the two planes, the wiring between A and B detours to the peripheral of the die to reach the bonding wires or solder balls, even when A and B are physically close in the vertical dimension.

Figure 2.2: Inter-chip interconnects in different 3D integration technologies: (a) Wire bonding based SiP, (b) solder balls based SiP, and (c) TSV-based 3D IC.

Alternatively, in TSV-based 3D ICs, the communication between multiple dies is achieved by high density vertical TSVs. Due to the relatively small dimension of TSVs, a large number of TSVs can be placed throughout the entire die area. Therefore, as shown in Fig 2.2(c), to connect circuit blocks A and B, the wiring can go through a nearby TSV, instead of the longer distance toward the peripheral of the die. The vertical TSVs are fabricated with conductive materials with low resistivity, as introduced later. Therefore, the total impedance of inter-plane connections is significantly reduced in TSV-based 3D ICs. In MIV-based 3D ICs, connection topology of the MIVs is similar to TSVs, expect that the MIVs are smaller in size and therefore able to achieve fine-grained vertical connections. However, the MIV-based 3D ICs could not support a large number of tiers integrated vertically, due to the monolithic fabrication process, making it a less applicable solution than TSV-based 3D ICs for heterogenous systems integration.

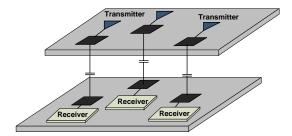

In contactless coupled 3D ICs, the physical vertical vias are replaced by the coupling of electric or magnetic fields. Specifically, in capacitively coupled 3D integration, small on-chip parallel capacitors are placed on each plane, as shown in

Figure 2.3: Capacitively coupled 3D integration.

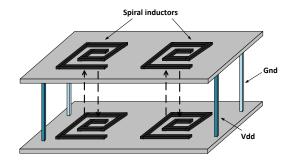

Figure 2.4: Inductively coupled 3D integration.

Fig. 2.3 [9]. Transmitter and receiver modules are required to drive the capacitors as well as modulate the received signals. Alternatively, in inductively coupled 3D ICs, spiral inductors are placed on each plane, as illustrated in Fig. 2.4 [9]. Specialized circuits are needed for transmitting and receiving signals. A common problem for the capacitively coupled and inductively coupled 3D ICs is the area overhead in fabricating the on-die capacitors and inductors, especially when CMOS technology is used where the fabrication of on-die capacitor and inductor is relatively area inefficient. Furthermore, the transmitter and receiver circuitry also consume power. Therefore, TSV-based 3D integration has been considered as the most promising approach in near future technology nodes.

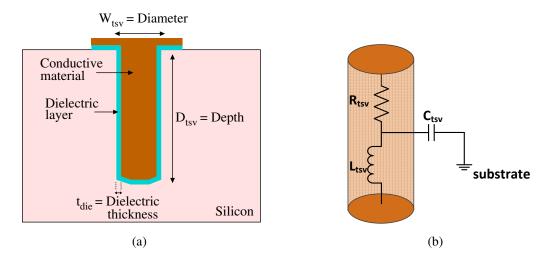

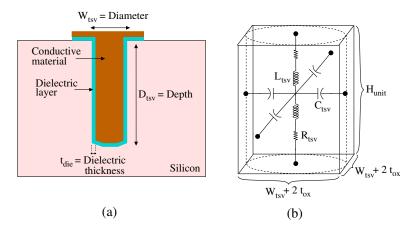

### 2.1.1 TSV Structure and Parasitic Impedance

In TSV-based 3D ICs, multiple dies are stacked vertically while TSVs are the critical components that connect multiple dies in a 3D stack. As indicated by its name (through silicon via), TSVs are long vertical vias etched within the silicon substrate, as illustrated in Fig. 2.5(a). Conductive materials, such as polysilicon, tungsten or copper, are used to fill the etched vias. To prevent the conductive filling material from diffusing into the silicon substrate during the fabrication process, there is a dielectric insulation layer surrounding the TSVs [30]. The TSV physical characteristics such as depth, diameter, dielectric thickness are determined by the TSV fabrication technology, as introduced in the following section.

In 3D ICs with high integration level, thousands of TSVs are placed to provide vertical connections among the planes [31] [32]. These TSVs are utilized for different purposes, including distributing the power supply voltage (power TSVs), clock signal distribution (clock TSVs), as well as the communication between modules on different planes (signal TSVs). Therefore, it is important to reduce the parasitic impedance of the TSVs to achieve enhanced connectivity.

The parasitic impedance of a TSV consists of parasitic resistance  $R_{tsv}$ , parasitic inductance  $L_{tsv}$ , and parasitic capacitance  $C_{tsv}$ , as illustrated in Fig. 2.5(b) [33]. Various methods have been proposed to characterize the parasitic impedances of a TSV from both measurement and theoretical analysis [33–36]. The parasitic resistance and inductance are primarily determined by the TSV dimensions and filling material. Typically, a TSV is represented as a cylinder with a diameter W and depth D. The dielectric insulation, which is typically an oxide layer, has a thickness of  $t_{ox}$ . Therefore, the parasitic resistance  $R_{tsv}$  and inductance  $L_{tsv}$  can be estimated using the resistivity and permeability of the filling material and TSV dimensions [37]. The

Figure 2.5: TSV characteristics: (a) cross-section of a TSV consisting of a conductive material and dielectric layer, (b) electrical model of a TSV illustrating the parasitic impedances.

parasitic capacitance  $C_{tsv}$  has two components: oxide capacitance and depletion capacitance. The oxide capacitance can be determined using the cylindrical capacitor formula [38]. When the TSV is charged at a bias voltage, there is also a depletion capacitance in series with the oxide capacitance [34]. A detailed method of estimating the parasitic impedances of a TSV with a distributed model is described in Chapter 6.

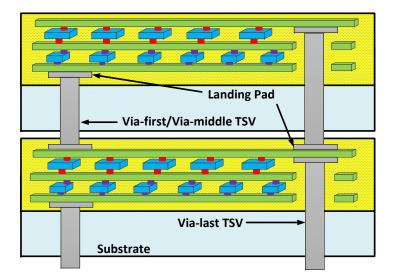

### 2.1.2 TSV Fabrication Technologies

In the process flow of TSV-based 3D ICs, the initial step is preparing the wafers to be bonded together. Each individual wafer is processed separately, which becomes a single plane of the 3D stack. During the wafer preparation, a certain amount of substrate area is reserved for TSVs. Deep reactive ion etching (DRIE) is used to etch the deep interplane vias within the silicon substrate [9]. These deep vias are later filled with conductive materials to form the TSVs. Depending on when the TSVs are formed in the process flow, TSV fabrication technologies can be categorized into via-first TSV, via-middle TSV, and via-last TSV technologies [39].