# Leveraging Monolithic 3D Integrated Circuit Technology for Emerging Applications

A Dissertation Presented

by

Chen Yan

to

The Graduate School

in Partial Fulfillment of the

Requirements

for the Degree of

**Doctor of Philosophy**

in

**Electrical Engineering**

Stony Brook University

December 2018

### **Stony Brook University**

The Graduate School

### Chen Yan

We the dissertation committee for the above candidate for the Doctor of Philosophy degree, hereby recommend acceptance of this dissertation.

Dr. Emre Salman - Advisor of Dissertation Associate Professor, Department of Electrical and Computer Engineering

Dr. Milutin Stanacevic - Chairperson of Defense Associate Professor, Department of Electrical and Computer Engineering

Dr. Peter Milder - Defense Committee Member Associate Professor, Department of Electrical and Computer Engineering

Dr. Qiaoyan Yu - Defense Committee Member Associate Professor, Department of Electrical and Computer Engineering, University of New Hampshire

This dissertation is accepted by the Graduate School

Richard Gerrig

Dean of the Graduate School

### Abstract of the Dissertation

# Leveraging Monolithic 3D Integrated Circuit Technology for Emerging Applications

by

### Chen Yan

### **Doctor of Philosophy**

in

### **Electrical Engineering**

Stony Brook University

#### 2018

Three-dimensional (3D) integrated circuits (ICs) have emerged as a practical solution to some of the critical issues encountered in planar technologies such as longer global interconnects and difficulty in scaling the transistors. Through-silicon via (TSV) based 3D ICs have attracted significant attention during the past decade with emphasis on both fabrication and design methodologies. However, a typical TSV diameter is in the range of several micrometers, which is multiple orders of magnitude larger than nanoscale transistor dimensions. Thus, bulky TSVs not only restrict the integration density, but also limit the power and performance advantages of vertical integration due to significant TSV capacitance. More recently, interest on monolithic 3D integration has grown due to encouraging developments on sequentially fabricating multiple transistor layers on a single substrate.

In monolithic vertical integration, stacked transistors are sequentially fabricated after the bottom layers have been manufactured. Communication among the tiers is achieved by monolithic inter-tier vias (MIVs). MIVs have comparable size to conventional on-chip metal vias since multiple tiers can be aligned with lithographic alignment precision. Thus, MIV based 3D integration enables significantly higher interconnect density as compared to TSV based vertical integration.

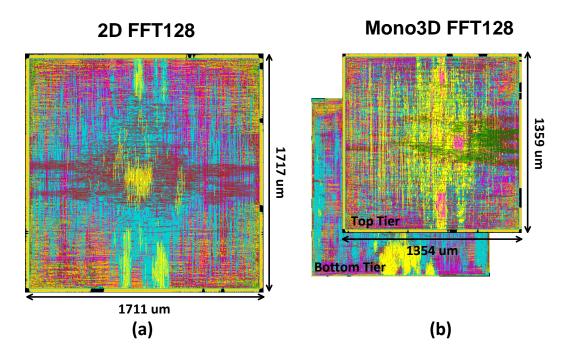

In this dissertation, an open source cell library based on a full custom design of each cell as well as a fully functional process design kit (PDK) are developed for transistor-level monolithic 3D integration technology. The power and timing characteristics of each cell are fully characterized with both SPICE-level simulations and a commercial library characterization tool to ensure accuracy. The proposed cell library is used to evaluate the power and timing characteristics of multiple benchmark circuits and a large scale 128-point FFT core with approximately 330K cells. Experimental results demonstrate that at a clock frequency of 1.5GHz, the FFT core implemented with the proposed monolithic 3D library consumes 51% less footprint as compared to conventional 2D technology. The 20% reduction in wirelength enables approximately 22% reduction in net switching power. The entire proposed library and related files for tool integration are publicly available to facilitate future research.

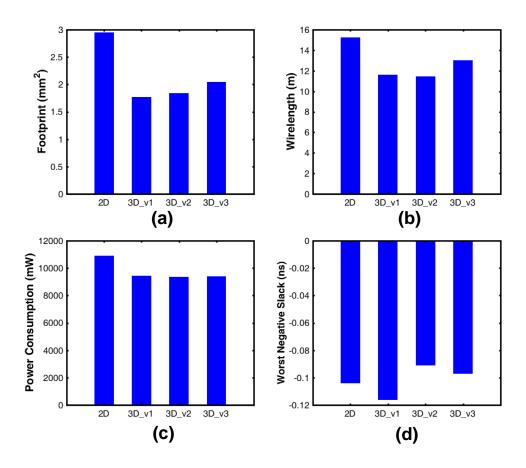

The effect of routing congestion on timing characteristics is stronger in monolithic 3D technology due to the significant reduction in footprint. Routing congestion increases the communication latency, thus degrades the quality of the IC. The cell-level number of routing tracks plays an essential role in routing congestion. Three versions of the cell library with different heights are developed to investigate the effect of the number of routing tracks on area, power, and delay characteristics. Simulation results of a large FFT core demonstrate that an optimum number of routing tracks exists which achieves 14% and 12.5% reduction in, respectively, overall power consumption and worst negative slack as compared to the conventional 2D technology, while consuming 38% less physical area. Clock tree characteristics of the large FFT core are also investigated.

The security of integrated circuits has emerged as a fundamental issue due to the threats from the globalized semiconductor supply chain. Monolithic 3D integrated circuits enable not only ultra-high density device integration, but also introduce novel opportunities and challenges on managing hardware security. The proposed PDK and cell library are used to develop an efficient logic camouflaging method for monolithic 3D ICs. Logic camouflaging is a layout-level technique to thwart image analysis based reverse engineering attacks. Full custom cell libraries are developed and characterized to camouflage large-scale 2D and 3D circuits. The methodology

is implemented and evaluated using a SIMON block cipher and several ISCAS'89 benchmark circuits.

Thermal management of monolithic 3D ICs is more challenging than 2D circuits due to the reduced circuit area (hence, higher power density) and the low thermal conductivity of the inter-layer dielectric material, situated between adjacent device layers. Therefore, accurate and efficient analysis of the thermal behavior is crucial for the reliability of monolithic 3D ICs. To determine the heat propagation and track the formation of hot spots, the thermal integrity of monolithic 3D circuits is explored at the physical level. Results demonstrate that the steady-state temperature increases by approximately 2 to 4 °C in monolithic 3D circuits as compared to the conventional 2D technology. The increase in temperature is not as significant due to two primary factors: (1) additional process layers in monolithic 3D technology are sufficiently thin, (2) power consumption is reduced by approximately 10%.

The proposed open source monolithic 3D process design kit and related design guidelines described in this dissertation provide significant insight into important characteristics of monolithic 3D ICs, such as 1) footprint, timing and power consumption, 2) routing congestion, 3) the effect of the number of routing tracks in each cell, 4) circuit camouflaging for security, and 5) thermal management.

# **Table of Contents**

| A۱ | bstrac  | et            |            |                                        | vi    |

|----|---------|---------------|------------|----------------------------------------|-------|

| Li | st of l | Figures       |            |                                        | xiii  |

| Li | st of ' | <b>Fables</b> |            |                                        | xvi   |

| A  | cknov   | vledgem       | nents      |                                        | xviii |

| 1  | Intr    | oductio       | n          |                                        | 1     |

| 2  | Bacl    | kgroun        | d          |                                        | 5     |

|    | 2.1     | Three-        | Dimensio   | nal Integration                        | . 5   |

|    |         | 2.1.1         |            | eturing Technologies for 3D ICs        |       |

|    |         |               | 2.1.1.1    | System-in-Package                      | . 7   |

|    |         |               | 2.1.1.2    | 3D ICs with Through-Silicon Vias (TSV) | . 9   |

|    |         |               | 2.1.1.3    | Monolithic 3D ICs                      | . 9   |

|    |         |               | 2.1.1.4    | Contactless 3D ICs                     | . 12  |

|    |         | 2.1.2         | Design I   | Methodologies for Monolithic 3D ICs    | . 13  |

|    |         |               | 2.1.2.1    | Transistor-level Monolithic 3D ICs     | . 13  |

|    |         |               | 2.1.2.2    | Gate-level Monolithic 3D ICs           | . 13  |

|    |         |               | 2.1.2.3    | Block-level Monolithic 3D ICs          | . 15  |

|    | 2.2     | Existin       | ng Researd | ch on Monolithic 3D ICs                | . 16  |

|    |         | 2.2.1         | Fabricat   | ion-Level Research                     | . 16  |

|    |         | 2.2.2         | Design-    | Level Research                         | . 16  |

| 3  | Mor     | 103D: C       | pen Sour   | ce Cell Library for Monolithic 3D ICs  | 20    |

|    | 3.1     | Open S        | Source Ce  | ll Library for Monolithic 3D ICs       | . 21  |

|    |         | 3.1.1         | Library    | Development                            | . 21  |

|    |         | 3.1.2         | Design I   | Flow                                   | . 25  |

|   | 3.2 |                                                       | ation Results                                               |

|---|-----|-------------------------------------------------------|-------------------------------------------------------------|

|   |     | 3.2.1                                                 | Cell-Level Evaluation                                       |

|   |     |                                                       | 3.2.1.1 Area                                                |

|   |     |                                                       | 3.2.1.2 Delay and Power Consumption 29                      |

|   |     | 3.2.2                                                 | System-Level Evaluation                                     |

|   |     |                                                       | 3.2.2.1 Footprint and Wirelength                            |

|   |     |                                                       | 3.2.2.2 Power Characteristics                               |

|   |     |                                                       | 3.2.2.3 Timing Characteristics                              |

|   | 3.3 | Summ                                                  | ary                                                         |

| 4 | Rou | ting Co                                               | ngestion in Monolithic 3D ICs 39                            |

|   | 4.1 | _                                                     | butions of This Work                                        |

|   | 4.2 |                                                       | g Congestion Aware Cell Library for Monolithic 3D ICs 40    |

|   | 4.3 |                                                       | mental Results                                              |

|   |     | 4.3.1                                                 | Cell-Level Evaluation                                       |

|   |     |                                                       | 4.3.1.1 Area                                                |

|   |     |                                                       | 4.3.1.2 Delay and Power Consumption                         |

|   |     | 4.3.2                                                 | System-Level Evaluation                                     |

|   | 4.4 |                                                       | ary                                                         |

|   |     | Summ                                                  | <u></u>                                                     |

| 5 | Har | Efficient Logic Camouflaging for Monolithic 3D ICs 55 |                                                             |

|   | 5.1 | Backg                                                 | round and Contributions                                     |

|   |     | 5.1.1                                                 | Circuit Camouflaging                                        |

|   |     | 5.1.2                                                 | Contributions of This Work                                  |

|   | 5.2 | Logic                                                 | Camouflaging for Monolithic 3D ICs                          |

|   |     | 5.2.1                                                 | Camouflaged Cells in 2D and Monolithic 3D Technologies . 60 |

|   |     | 5.2.2                                                 | Cell-Level Evaluation 62                                    |

|   |     |                                                       | 5.2.2.1 Footprint                                           |

|   |     |                                                       | 5.2.2.2 Delay and Power Consumption 64                      |

|   | 5.3 | Chip-I                                                | Level Simulation Results                                    |

|   |     | 5.3.1                                                 | Experimental Setup                                          |

|   |     | 5.3.2                                                 | System-Level Evaluation                                     |

|   |     |                                                       | 5.3.2.1 Footprint and Wirelength 67                         |

|   |     |                                                       | 5.3.2.2 Power Characteristics 69                            |

|   |     |                                                       | 5.3.2.3 Timing Characteristics                              |

|   |     | C                                                     | 72                                                          |

| 6  | The   | rmal M                            | anagement and Analy   | ysis of Monolithic 3D ICs |  | <b>74</b> |

|----|-------|-----------------------------------|-----------------------|---------------------------|--|-----------|

|    | 6.1   | Backg                             | ound and Contribution | ns                        |  | . 75      |

|    |       | 6.1.1                             | Thermal Managemen     | ıt                        |  | . 75      |

|    |       |                                   | 6.1.1.1 Thermal Is    | sues in Monolithic 3D ICs |  | . 75      |

|    |       |                                   | 6.1.1.2 Full-Chip 7   | Thermal Analysis          |  | . 76      |

|    |       | 6.1.2                             | Contributions of This | Work                      |  | . 77      |

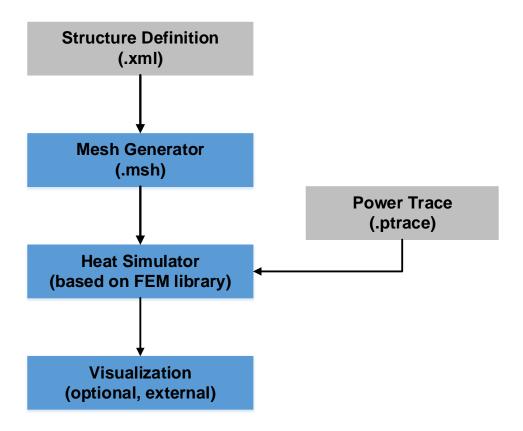

|    | 6.2   | Propos                            | ed Thermal Analysis F | Flow                      |  | . 77      |

|    |       | 6.2.1                             |                       | Review                    |  |           |

|    |       |                                   | 6.2.1.1 Standard C    | ell Timing Modeling       |  | . 78      |

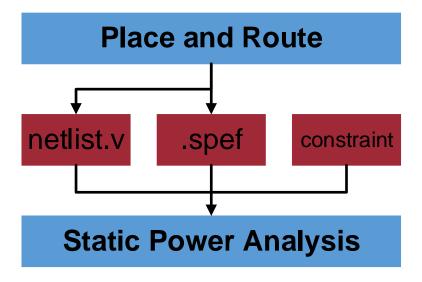

|    |       |                                   | 6.2.1.2 Standard C    | ell Power Modeling        |  | . 79      |

|    |       | 6.2.2                             | Thermal Analysis Flo  | ow                        |  | 81        |

|    |       |                                   | 6.2.2.1 Thermal A     | nalyzer Introduction      |  | 81        |

|    |       |                                   | 6.2.2.2 Thermal A     | nalysis Data Flow         |  | 83        |

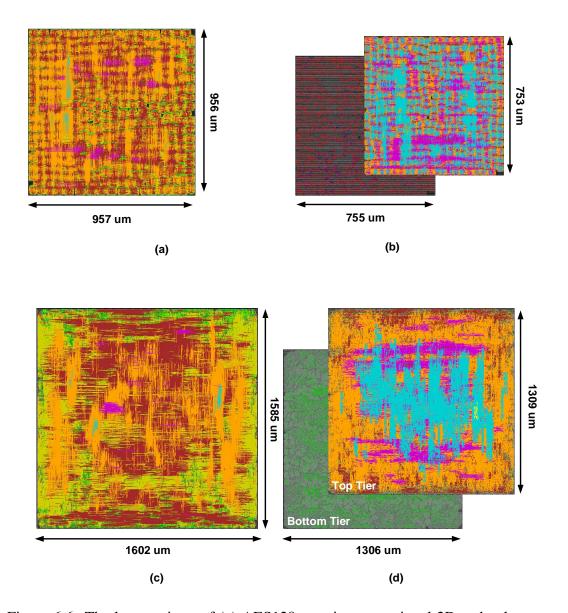

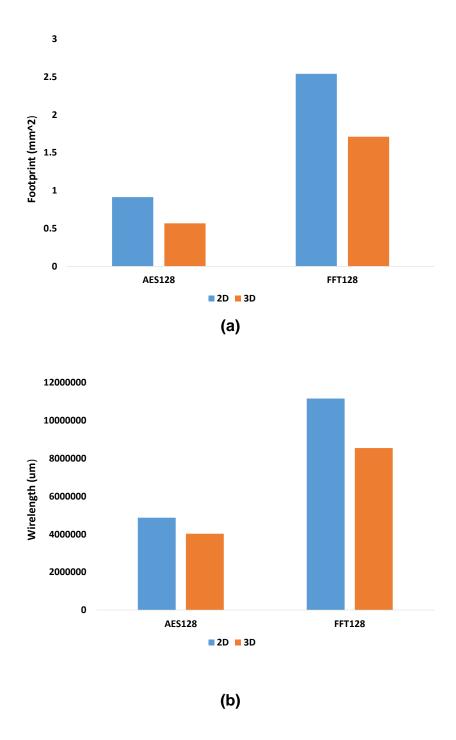

|    | 6.3   | Simula                            | tion Results          |                           |  | . 88      |

|    |       | 6.3.1                             | Footprint and Power   |                           |  | 89        |

|    |       |                                   | 6.3.1.1 Footprint.    |                           |  | 89        |

|    |       |                                   | 6.3.1.2 Power         |                           |  | 92        |

|    |       | 6.3.2                             | Temperature           |                           |  | 93        |

|    | 6.4   | Summ                              | ary                   |                           |  | 96        |

| 7  | Con   | Conclusions and Future Directions |                       |                           |  |           |

|    | 7.1   | Thesis                            | Summary               |                           |  | 97        |

|    | 7.2   |                                   |                       |                           |  |           |

| Bi | bliog | raphy                             |                       |                           |  | 100       |

# **List of Figures**

| 1.1 | Summary of the contributions                                                                                                                                                                                               | 2  |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Reduction in wirelength where the conventional 2D circuit is implemented in two planes: (a) Planar integrated circuit with an area <i>A</i> , (b) Two-plane 3D integrated circuit with an area <i>A</i> /2 for each plane. | 6  |

| 2.2 | Examples of SiP: (a) wire-bonded SiP [1], (b) solder balls at the perimeter of the planes [2], (c) area array vertical interconnects, and (d) interconnects on the force of the SiP [3]                                    | 8  |

| 2.3 | and (d) interconnects on the faces of the SiP [3]                                                                                                                                                                          | 10 |

| 2.4 | nology [4]                                                                                                                                                                                                                 | 11 |

| 2.5 | Contactless 3D integrated circuits: (a) capacitively coupled 3D integration, (b) inductively coupled 3D integration.                                                                                                       | 12 |

| 2.6 | Design methodology for monolithic 3D technology: transistor-level monolithic 3D.                                                                                                                                           | 14 |

| 2.7 | Design methodology for monolithic 3D technology: gate-level monolithic 3D.                                                                                                                                                 | 14 |

| 2.8 | Design methodology for monolithic 3D technology: block-level monolithic 3D.                                                                                                                                                | 15 |

| 2.9 | Cross sectional image of two stacked devices fabricated through monolithic 3D integration technology [5]                                                                                                                   | 17 |

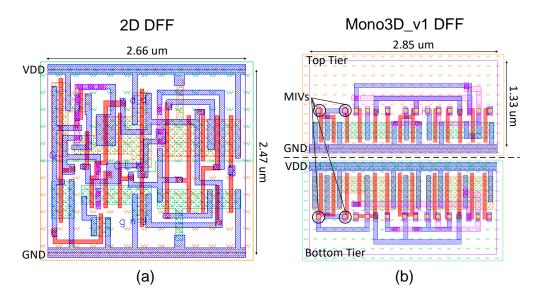

| 3.1 | Cross-sections of the conventional 2D and transistor-level monolithic (TL-Mono) 3D technology with two tiers. The top tier hosts the nMOS transistors whereas the pMOS transistors are placed within the bottom tier.      | 22 |

| 3.2 | Comparison of the layout views of a NAND gate in (a) traditional                                                                                                                                                                                                                     |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | 2D technology with 14 routing tracks in each cell, (b) monolithic                                                                                                                                                                                                                    |    |

|     | 3D technology with 9 routing tracks, illustrating the three MIVs used to connect the top and bottom tiers                                                                                                                                                                            | 24 |

| 3.3 | Comparison of the layout views of a D-flip-flop in traditional 2D                                                                                                                                                                                                                    | 24 |

| 3.3 | and transistor-level monolithic 3D technology. The top and bottom tiers are separately depicted for the 3D technology                                                                                                                                                                | 25 |

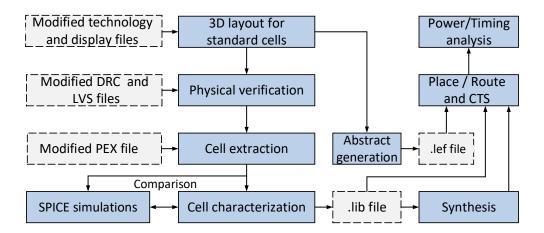

| 3.4 | Integration of the proposed open source cell library into design flow,                                                                                                                                                                                                               | 23 |

|     | illustrating the required modifications                                                                                                                                                                                                                                              | 26 |

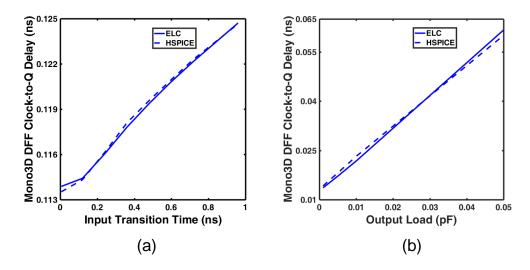

| 3.5 | Comparison of the automated cell library characterization process with <i>HSPICE</i> simulations: (a) clock-to-Q delay of a 3D D-flip-flop as a function of input transition time at constant load capacitance of 0.01 pF, (b) clock-to-Q delay of a 3D D-flip-flop as a function of |    |

|     | load capacitance at constant input transition time of 120 ps                                                                                                                                                                                                                         | 27 |

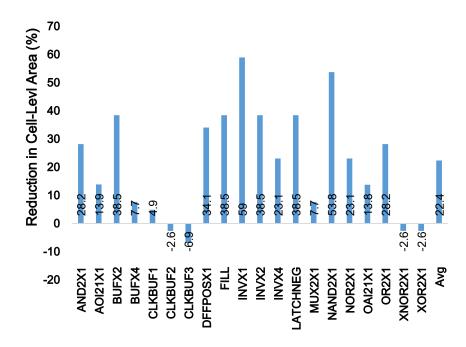

| 3.6 | Percent reduction in area achieved by each monolithic 3D cell as                                                                                                                                                                                                                     |    |

|     | compared to the 2D cells. Results are provided for the 3D library,                                                                                                                                                                                                                   |    |

|     | Mono3D                                                                                                                                                                                                                                                                               | 28 |

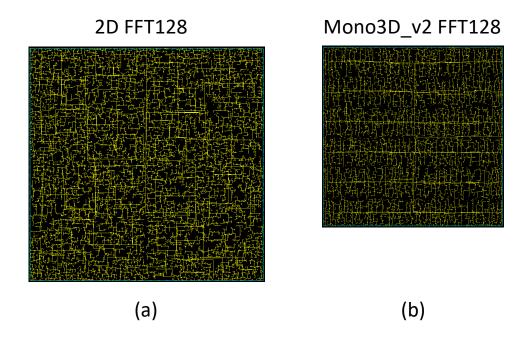

| 3.7 | The layout views of a highly parallelized 128-point FFT core in (a) conventional 2D technology with 14 routing tracks in each cell, (b)                                                                                                                                              |    |

|     | transistor-level monolithic 3D technology                                                                                                                                                                                                                                            | 34 |

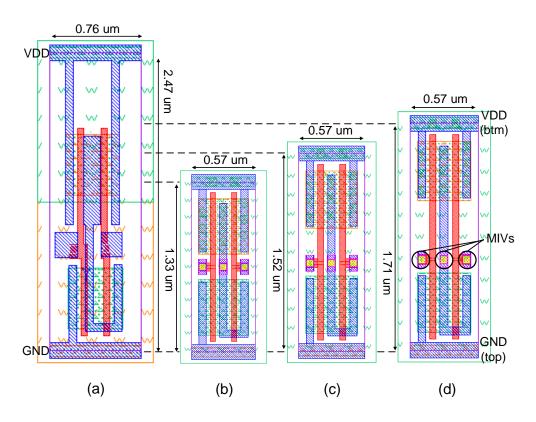

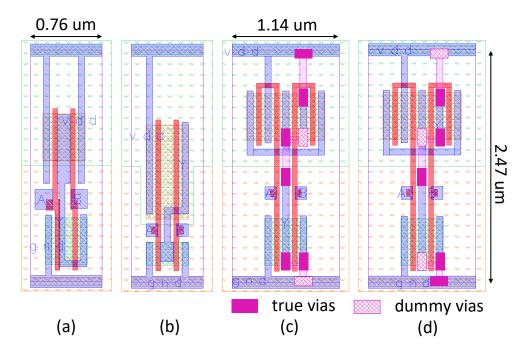

| 4.1 | Comparison of the layout views of a NAND gate in (a) traditional                                                                                                                                                                                                                     |    |

|     | 2D technology with 14 routing tracks in each cell, (b) monolithic 3D technology with 8 routing tracks, (c) monolithic 3D technology with 9 routing tracks, and (d) monolithic 3D technology with 10 routing tracks, illustrating the three MIVs used to connect the top              |    |

|     | and bottom tiers                                                                                                                                                                                                                                                                     | 42 |

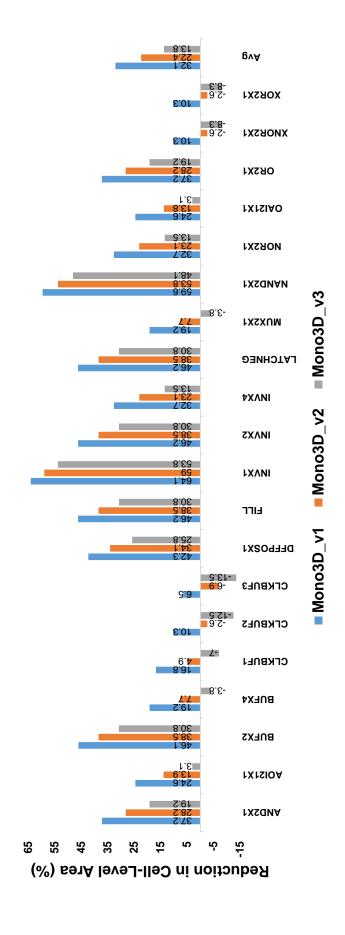

| 4.2 | Percent reduction in area achieved by each individual monolithic                                                                                                                                                                                                                     |    |

|     | 3D cell as compared to the 2D cells. Results are provided for each                                                                                                                                                                                                                   |    |

| 4.2 | 3D library, $Mono3D_{-}v1$ , $Mono3D_{-}v2$ , and $Mono3D_{-}v3$                                                                                                                                                                                                                     | 44 |

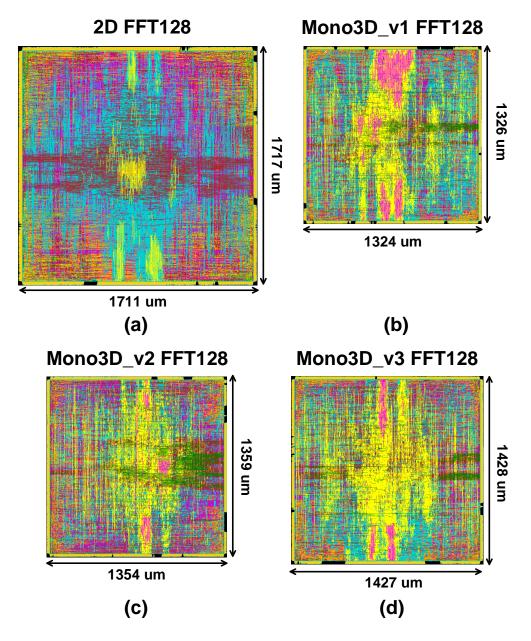

| 4.3 | The layout views of a highly parallelized 128-point FFT core in (a) conventional 2D technology with 14 routing tracks in each cell, (b)                                                                                                                                              |    |

|     | transistor-level monolithic 3D technology with 8 routing tracks, (c)                                                                                                                                                                                                                 |    |

|     | monolithic 3D technology with 9 routing tracks, and (d) monolithic                                                                                                                                                                                                                   |    |

|     | 3D technology with 10 routing tracks                                                                                                                                                                                                                                                 | 48 |

| 4.4 | Summary of results obtained from the FFT128 operating at 1.5                                                                                                                                                                                                                         |    |

|     | GHz: (a) footprint, (b) wirelength, (c) power consumption, and (d)                                                                                                                                                                                                                   |    |

|     | worst negative slack                                                                                                                                                                                                                                                                 | 51 |

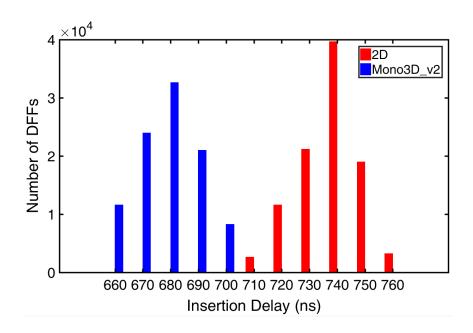

| 4.5                               | Clock tree floorplan of a 128-point FFT core with approximately 97K flip-flops: (a) traditional 2D technology and (b) monolithic 3D technology with 9 routing tracks in each cell ( <i>Mono3D_v2</i> ) | 52         |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 4.6                               | Comparison of clock insertion delay histograms for 2D FFT and monolithic 3D FFT                                                                                                                        | 53         |

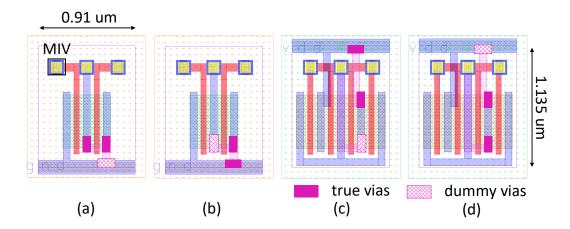

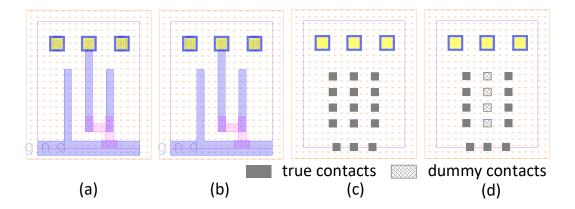

| 5.1                               | Standard cell layouts in 2D technology: (a) conventional NAND, (b) conventional NOR, (c) camouflaged NAND, and (d) camou-                                                                              | <b>~</b> c |

| <b>7</b> 0                        | flaged NOR                                                                                                                                                                                             | 58         |

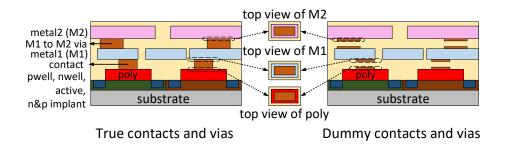

| <ul><li>5.2</li><li>5.3</li></ul> | Illustration of true and dummy contacts/vias                                                                                                                                                           | 58         |

| 5.4                               | gate, (d) bottom tier of NOR gate                                                                                                                                                                      | 60         |

|                                   | flaged monolithic 3D cells: (a) NAND metal layers, (b) NOR metal                                                                                                                                       |            |

|                                   | layers, (c) NAND contacts, (d) NOR contacts                                                                                                                                                            | 62         |

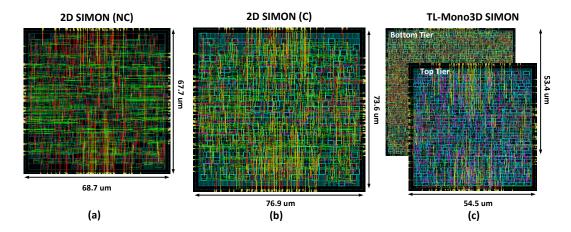

| 5.5                               | The layout views of SIMON cipher in (a) conventional 2D technology without camouflaging, (b) conventional 2D technology with                                                                           |            |

|                                   | camouflaging, (c) transistor-level monolithic 3D technology with                                                                                                                                       |            |

|                                   | camouflaging                                                                                                                                                                                           | 68         |

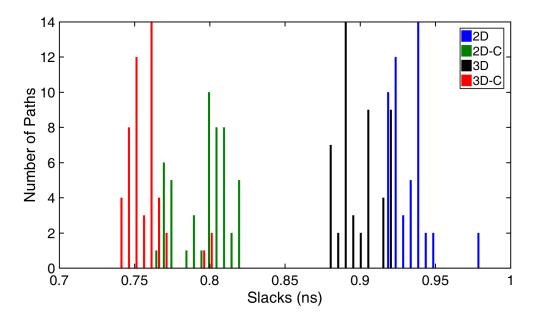

| 5.6                               | Slack distribution of the 50 slowest paths in SIMON cipher for 2D technology without (2D) and with (2D-C) camouflaging, and                                                                            |            |

|                                   | monolithic 3D technology without (3D) and with camouflaging (3D-                                                                                                                                       |            |

|                                   | C)                                                                                                                                                                                                     | 72         |

| 6.1                               | The MTA flow with user-supplied input files highlighted in grey [6].                                                                                                                                   | 82         |

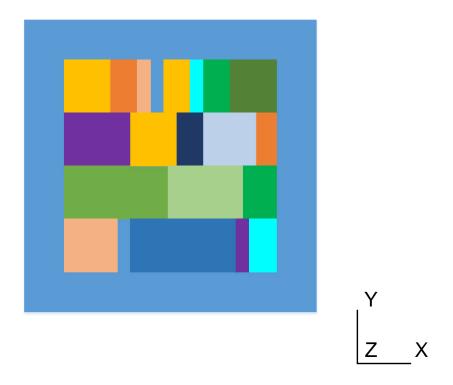

| 6.2                               | Computation mesh of ISCAS'89 s27 generated by MTA                                                                                                                                                      | 84         |

| 6.3                               | Static power analysis data flow                                                                                                                                                                        | 86         |

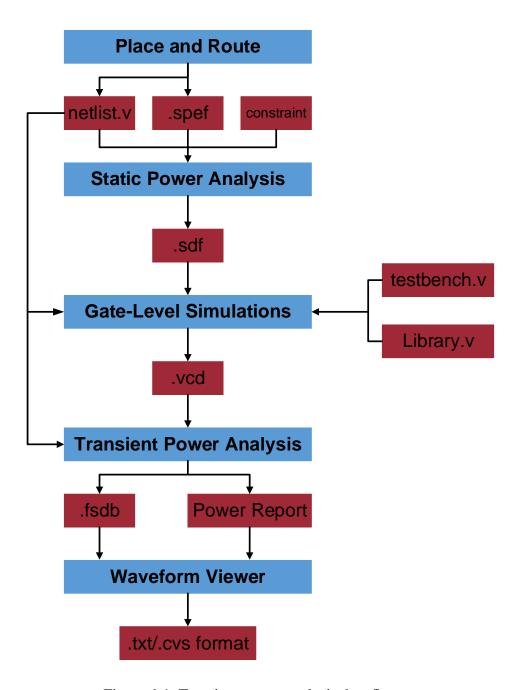

| 6.4                               | Transient power analysis data flow                                                                                                                                                                     | 87         |

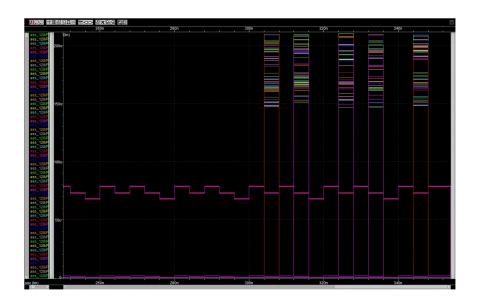

| 6.5                               | Transient power waveform of AES128                                                                                                                                                                     | 88         |

| 6.6                               | The layout views of (a) AES128 core in conventional 2D technol-                                                                                                                                        |            |

|                                   | ogy, (b) AES128 core in transistor-level monolithic 3D technology,                                                                                                                                     |            |

|                                   | (c) FFT128 core in conventional 2D technology, (d) FFT128 core                                                                                                                                         | 0.0        |

| 67                                | in transistor-level monolithic 3D technology                                                                                                                                                           | 90         |

| 6.7                               | The footprint and wirelength comparison of AES128 and FFT128 cores in conventional 2D technology and transistor-level monolithic                                                                       |            |

|                                   | 3D technology.                                                                                                                                                                                         | 91         |

|                                   |                                                                                                                                                                                                        |            |

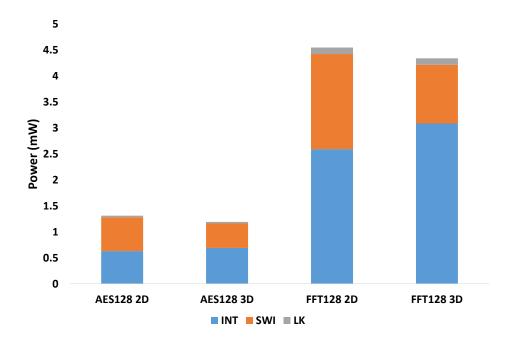

| 6.8  | The power comparison of AES128 and FFT128 cores in conven-          |    |

|------|---------------------------------------------------------------------|----|

|      | tional 2D technology and transistor-level monolithic 3D technol-    |    |

|      | ogy. INT, SWI, and LK refer, respectively, to internal, switching   |    |

|      | (net), and leakage power                                            | 92 |

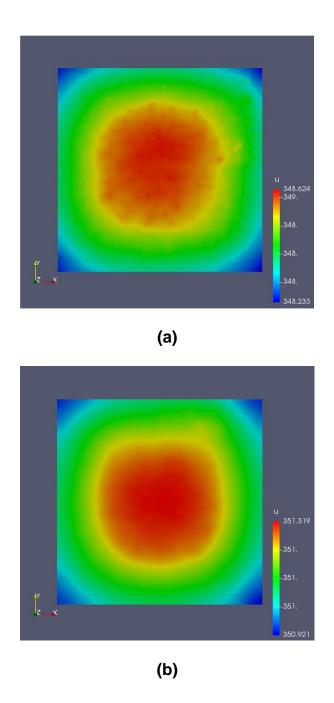

| 6.9  | Spatial temperature distribution of AES128 core in (a) conventional |    |

|      | 2D technology, (b) in transistor-level monolithic 3D technology     | 94 |

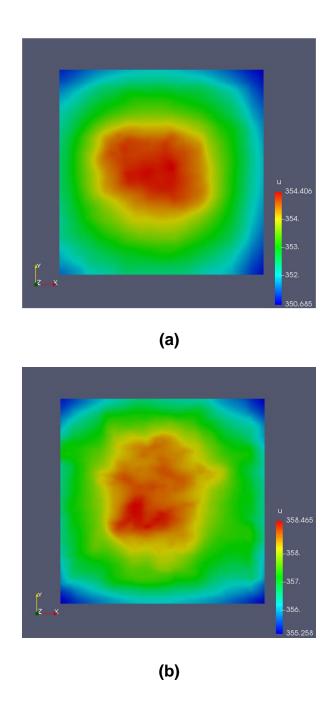

| 6.10 | Spatial temperature distribution of FFT128 core in (a) conventional |    |

|      | 2D technology, (b) in transistor-level monolithic 3D technology     | 95 |

|      |                                                                     |    |

# **List of Tables**

| 3.1 | List of standard cells in the monolithic 3D library                        | 23 |

|-----|----------------------------------------------------------------------------|----|

| 3.2 | Average delay and power characteristics of 2D and monolithic 3D            |    |

|     | cells with 9 (Mono3D) routing tracks. The percent changes with             |    |

|     | respect to 2D cells are listed                                             | 30 |

| 3.3 | Number and type of cells for each benchmark circuit operating at           |    |

|     | 500 MHz                                                                    | 31 |

| 3.4 | Number and type of cells for each benchmark circuit operating at           |    |

|     | 1.5/2 GHz                                                                  | 32 |

| 3.5 | Comparison of footprint, wirelength, and the number of DRC viola-          |    |

|     | tions (vios) in 2D and monolithic 3D technologies with 9 (Mono3D)          |    |

|     | routing tracks in each 3D cell, operating at 500 MHz. The percent          |    |

|     | changes with respect to 2D cells are listed                                | 33 |

| 3.6 | Comparison of footprint, wirelength, and the number of DRC viola-          |    |

|     | tions (vios) in 2D and monolithic 3D technologies with 9 (Mono3D)          |    |

|     | routing tracks in each 3D cell, operating at 1.5/2 GHz. The percent        |    |

|     | changes with respect to 2D cells are listed                                | 33 |

| 3.7 | Comparison of power consumption in 2D and monolithic 3D tech-              |    |

|     | nologies 9 routing tracks in each cell, operating at 500 MHz. <i>INT</i> , |    |

|     | SWI, and LK refer, respectively, to internal, switching (net), and         |    |

|     | leakage power.                                                             | 34 |

| 3.8 | Comparison of power consumption in 2D and monolithic 3D tech-              |    |

|     | nologies with 9 routing tracks in each cell, operating at 1.5/2 GHz.       |    |

|     | INT, SWI, and LK refer, respectively, to internal, switching (net),        |    |

|     | and leakage power.                                                         | 35 |

| 3.9 | Comparison of timing characteristics in 2D and monolithic 3D tech-         |    |

|     | nologies with 9 routing tracks in each cell. WS, WNS, and TNS refer,       |    |

|     | respectively, to worst slack, worst negative slack, and total negative     |    |

|     | slack                                                                      | 37 |

| 4.1 | Average delay characteristics of 2D and monolithic 3D cells with 8 ( <i>Mono3D_v1</i> ), 9 ( <i>Mono3D_v2</i> ), and 10 ( <i>Mono3D_v3</i> ) routing tracks. |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | The percent changes with respect to 2D cells are listed                                                                                                      | 45 |

| 4.2 | Average power characteristics of 2D and monolithic 3D cells with 8                                                                                           | 13 |

|     | $(Mono3D_v I)$ , 9 $(Mono3D_v 2)$ , and 10 $(Mono3D_v 3)$ routing tracks.                                                                                    |    |

|     | The percent changes with respect to 2D cells are listed                                                                                                      | 46 |

| 4.3 | Comparison of the area, wirelength, and number of DRC viola-                                                                                                 |    |

|     | tions in 2D FFT and monolithic 3D FFT with 8 (Mono3D_v1),                                                                                                    |    |

|     | 9 (Mono3D_v2), and 10 (Mono3D_v3) routing tracks in each cell.                                                                                               |    |

|     | DRC vios refers to the number of design rule check (DRC) violations.                                                                                         | 47 |

| 4.4 | Comparison of power consumption in 2D FFT and monolithic 3D                                                                                                  |    |

|     | FFT with 8 ( $Mono3D\_v1$ ), 9 ( $Mono3D\_v2$ ), and 10 ( $Mono3D\_v3$ )                                                                                     |    |

|     | routing tracks in each cell, operating at 500 MHz. INT, SWI, and                                                                                             |    |

|     | LK refer, respectively, to internal, switching (net), and leakage power.                                                                                     | 49 |

| 4.5 | Comparison of power consumption in 2D FFT and monolithic 3D                                                                                                  |    |

|     | FFT with 8 $(Mono3D_v1)$ , 9 $(Mono3D_v2)$ , and 10 $(Mono3D_v3)$                                                                                            |    |

|     | routing tracks in each cell, operating at 1.5 GHz. <i>INT, SWI</i> , and <i>LK</i>                                                                           | 40 |

| 4.6 | refer, respectively, to internal, switching (net), and leakage power Comparison of timing characteristics in 2D FFT and monolithic 3D                        | 49 |

| 4.0 | FFT with 8 ( $Mono3D_v I$ ), 9 ( $Mono3D_v V$ 2), and 10 ( $Mono3D_v V$ 3)                                                                                   |    |

|     | routing tracks in each cell. WS, WNS and TNS refer, respectively, to                                                                                         |    |

|     | worst slack, worst negative slack and total negative slack                                                                                                   | 50 |

| 4.7 | Comparison of primary clock tree characteristics of 2D FFT and                                                                                               |    |

| ,   | monolithic 3D FFT                                                                                                                                            | 53 |

|     |                                                                                                                                                              |    |

| 5.1 | List of standard cells in the camouflaged 2D and monolithic 3D                                                                                               |    |

|     | libraries                                                                                                                                                    | 61 |

| 5.2 | Area, average delay and power characteristics of conventional 2D,                                                                                            |    |

|     | camouflaged 2D (2D_C), monolithic 3D, and camouflaged mono-                                                                                                  |    |

|     | lithic 3D (3D <sub>C</sub> ) standard cells. All of the percentages are with respect to conventional 2D results                                              | 63 |

| 5.3 | The overall number of gates and the distribution of camouflaged                                                                                              | 03 |

| 3.3 | and non-camouflaged cells. <i>NCC</i> , and <i>CC</i> refer, respectively, to                                                                                |    |

|     | Non-Camouflaged Cells, and Camouflaged Cells                                                                                                                 | 66 |

| 5.4 | Area and wirelength characteristics in conventional 2D, camou-                                                                                               | 50 |

|     | flaged 2D (2D_C), monolithic 3D, and camouflaged monolithic 3D                                                                                               |    |

|     | (3D <sub>-</sub> C) circuits. All of the percentages are with respect to conven-                                                                             |    |

|     | tional 2D results                                                                                                                                            | 68 |

| 5.5 | Comparison of power consumption in conventional 2D, camou-                             |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | flaged 2D (2D <sub>-</sub> C), monolithic 3D, and camouflaged monolithic 3D            |    |

|     | (3D <sub>-</sub> C) circuits. <i>INT</i> refers to interconnect power. All of the per- |    |

|     | centages are with respect to conventional 2D results                                   | 69 |

| 5.6 | Timing characteristics in conventional 2D, camouflaged 2D (2D <sub>-</sub> C),         |    |

|     | monolithic 3D, and camouflaged monolithic 3D circuits. All of the                      |    |

|     | percentages are with respect to conventional 2D results                                | 71 |

| 6.1 | Layer thicknesses in proposed monolithic 3D technology                                 | 83 |

| 6.2 | Comparison of footprint and wirelength in 2D with 14 routing tracks                    |    |

|     | and monolithic 3D technologies with 9 (Mono3D) routing tracks in                       |    |

|     | each 3D cell, operating at 250 MHz. The percent changes with                           |    |

|     | respect to 2D cells are listed                                                         | 89 |

| 6.3 | Comparison of power consumption in 2D and monolithic 3D tech-                          |    |

|     | nologies 9 routing tracks in each cell, operating at 250 MHz. INT,                     |    |

|     | SWI, and LK refer, respectively, to internal, switching (net), and                     |    |

|     | leakage power.                                                                         | 93 |

### ACKNOWLEDGEMENTS

First and foremost I would like to thank my advisor, Prof. Emre Salman. It has been such an honor to be his Ph.D. student. I appreciate all his tremendous contributions of time, ideas, and funding to make my Ph.D. career productive and memorable. Also, I want to express my sincere gratitude for his valuable feedback, advice, and encouragement, for his patience, motivation, and immense knowledge. I could not have imagined having a better advisor for my Ph.D. study. Thankful for him providing an excellent example as a successful researcher and professor.

Besides my advisor, I would like to thank my managers, Dr. Pengbo (Shelley) Sun and Alexander Martin, from GLOBALFOUNDRIES, who provided me with excellent internship opportunities. Special thanks to my mentors, Dr. Qi Qi, and Dr. Guoqing Deng, for their tremendous support. Also, profound gratitude goes to Prof. Qiaoyan Yu from University of New Hampshire, for her insightful discussions and ideas.

I am very thankful to all my defense committee: Prof. Sangjin Hong, Prof. Milutin Stanacevic, Prof. Peter Milder and Prof. Qiaoyan Yu, for their valuable comments and questions.

I owe a high debt of gratitude to all my fellow labmates in NanoCAS Labo-

ratory: Hailang, Zhihua, Weicheng, Tutu, Mallika, Manav, Ivan and Krithika for stimulating discussions, for the late nights we were working together before the deadlines and for the great times we shared in the last five and a half years. Thank you for making my Ph.D. life not only about simulations but also friendship. I wish all of you the best of luck and a bright future.

Last but not least, I would like to thank my family: my parents Xinmin Yan, Yingjie Liu and my partner Chris Perkins Yan for their endless emotional support and love throughout my Ph.D. career and my life in general. I dedicate this thesis to them.

## **Chapter 1**

## Introduction

Technology scaling has been a powerful driver for the continuous development of the microelectronics industry. However, conventional CMOS technologies face critical challenges as technology nodes keep shrinking, particularly below 10 and 7nm. Recently, several CMOS foundries decided to stop 7nm FinFET technology development [7–9], such as GLOBALFOUNDRIES (GF) [10] and United Microelectronics Corporation (UMC) [11]. 3D integrated circuits with through-silicon via (TSV) or wire bonding technology have been explored to enable the continuous growth in transistor density [12]. In TSV based 3D integration, multiple dies are thinned, aligned, and vertically bonded, thereby enabling shorter global interconnects (and therefore reduced power consumption) and heterogeneous integration [13].

Monolithic 3D integration has received growing attention due to ultra-high density device integration with the smallest vertical interconnects [14]. In monolithic vertical integration, stacked transistors are sequentially fabricated after the bottom layers have been manufactured. Communication among the tiers is achieved by

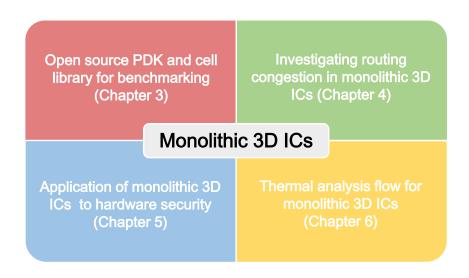

Figure 1.1: Summary of the contributions.

monolithic inter-tier vias (MIVs). MIVs have comparable size to conventional onchip metal vias since multiple tiers can be aligned with lithographic alignment precision [15]. Thus, MIV based 3D integration enables significantly higher interconnect density as compared to TSV based vertical integration.

A monolithic 3D standard cell library integrated into a conventional design flow is developed to facilitate the design process of complex ICs in monolithic 3D technology. Furthermore, the routing complexity increases in monolithic 3D ICs due to the significant reduction in footprint. Thus, routing congestion aware libraries are developed to mitigate this issue. Increasing power density leads to thermal issues in vertically integrated circuits. A thermal analysis flow is proposed to explore monolithic 3D heat dissipation. In addition to these challenges, 3D ICs introduce new opportunities on managing hardware security, such as split manufacturing techniques and logic camouflaging, as shown in this thesis. These challenges and opportunities are summarized in Chapter 2.

In this thesis, four contributions are proposed on monolithic 3D integration technology, as summarized in Figure 1.1. An open source cell library based on a full custom design of each cell is developed for transistor-level monolithic 3D integration [16] based on existing 2D 45 nm process design kit. The proposed cell library is used to evaluate the power and timing characteristics of multiple benchmark circuits and a large scale 256-point FFT core [17]. Multiple versions of the library with different cell heights are also developed to investigate the tradeoffs among routability, timing, power and area characteristics. This analysis is essential since routing congestion is one of the primary physical design issues in monolithic 3D ICs. Clock tree characteristics of the large FFT core are also investigated.

For 3D hardware security, an efficient logic camouflaging method for monolithic 3D ICs is presented. Full custom cell libraries are developed and fully characterized to camouflage large-scale 2D and 3D circuits. The area, power, and timing overhead of circuit camouflaging is evaluated both at the cell- and chip-levels.

Higher temperatures and thermal gradients are expected for 3D ICs due to increased power densities. An accurate exploration of the thermal behavior of monolithic 3D circuits is provided by combining the proposed cell library and a publicly available thermal simulator which supports cell-level analysis.

The rest of this thesis is organized as follows. Background on 3D ICs and existing works on monolithic 3D ICs are provided in Chapter 2. The proposed open source monolithic 3D standard cell library and process design kit are presented in Chapter 3. The proposed routing congestion aware monolithic 3D standard cell library is introduced in Chapter 4. The proposed hardware-efficient camouflaging methodology for monolithic 3D ICs is elaborated in Chapter 5. Explorations of the thermal behavior in monolithic 3D ICs and related analysis flow are described in

Chapter 6. Finally, the thesis is concluded in Chapter 7 with a brief discussion on future research directions.

## Chapter 2

## **Background**

As indicated by International Roadmap for Devices and Systems (IRDS) [18], after 2024, there will not be enough headroom for 2D geometry scaling. 3D ICs have emerged as a compelling solution for a portion of the issues experienced in planar technologies such as longer global interconnects and difficulty in scaling the transistors [19–21]. Vertical integration technologies are expected to be critical performance boosters, as predicted by IRDS [18]. Several different 3D manufacturing technologies are introduced in Section 2.1. Existing works on monolithic 3D ICs are summarized in Section 2.2.

### 2.1 Three-Dimensional Integration

3D ICs stack 2D dies along the vertical dimension. As compared to traditional 2D planar technologies, 3D ICs achieve significant benefits, such as smaller footprint, shorter interconnect, lower power consumption and higher communication bandwidth. Also, 3D ICs provide opportunities for highly heterogeneous and mul-

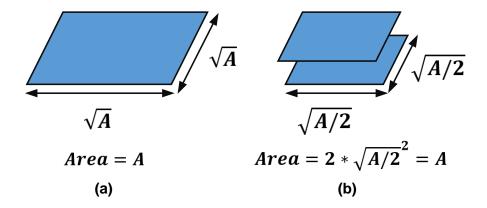

Figure 2.1: Reduction in wirelength where the conventional 2D circuit is implemented in two planes: (a) Planar integrated circuit with an area A, (b) Two-plane 3D integrated circuit with an area A/2 for each plane.

tifunctional systems and new hardware implementations for circuit security.

The core competitiveness of 3D integration is the decrease in the length of the longest interconnects within an IC [20]. As shown in Figure 2.1 (a), assuming a conventional 2D circuit with an area A, the longest interconnect in this planar IC has a length

$$L_{max,2D} = 2 \times \sqrt{A}. (2.1)$$

If the same circuit is implemented with two stacked dies with an area A/2 for each plane, the overall area of the system will not change, but the length of the longest interconnect for this 3D IC will be reduced to

$$L_{max,3D} = 2 \times \sqrt{A/2},\tag{2.2}$$

which is  $\sqrt{2}/2$  of  $L_{max,2D}$ . Therefore, by increasing the number of dies in a 3D IC,

the length of the longest interconnect can be further reduced.

### 2.1.1 Manufacturing Technologies for 3D ICs

There are two primary types of 3D IC manufacturing process: a sequential or a parallel process [20]. In the case of a parallel process, a 3D IC is manufactured by bonding multiple wafers or bare dies. Alternatively, in a sequential process, the devices and metal layers of the higher planes of the stack are fabricated layer by layer on top of the first plane.

3D ICs can be classified in terms of the level of vertical interconnect hierarchy. In general, 3D integration contains technologies such as system-in-package (SiP), through-silicon via (TSV)-based 3D integration, monolithic 3D integration, and contactless coupled 3D ICs.

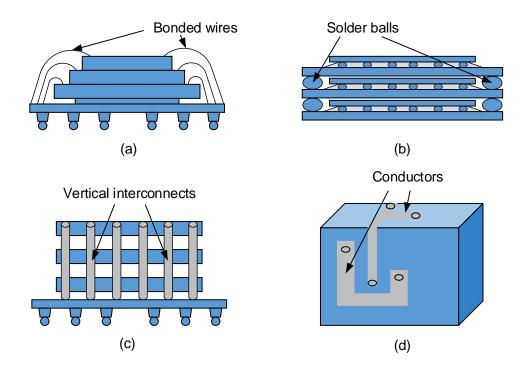

### 2.1.1.1 System-in-Package

A system-in-package (SiP) is a variety of ICs contained in a single package [22], where the interconnections of these circuits are implemented by the third dimension by using wire bonding, peripheral vertical interconnects, area array vertical interconnects, or metalization between the faces of a 3D stack, as shown in Figure 2.2 [20].

An SiP will considerably increase the packaging efficiency by improving the die-to-package area ratio and reducing the package footprint at the same time. Also, SiP provides a full commercialized variant of vertical integration. Thus, many firms have leveraged SiP products [3, 23].

Figure 2.2: Examples of SiP: (a) wire-bonded SiP [1], (b) solder balls at the perimeter of the planes [2], (c) area array vertical interconnects, and (d) interconnects on the faces of the SiP [3].

### 2.1.1.2 3D ICs with Through-Silicon Vias (TSV)

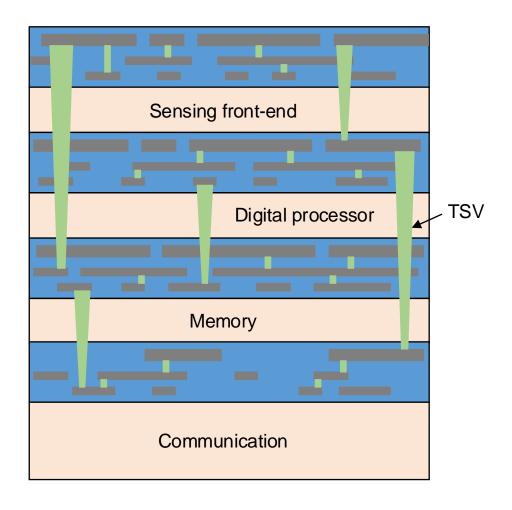

Through-silicon via (TSV) based 3D ICs have attracted vital attention throughout the past decade with emphasis on both fabrication and design methodologies [24–28]. In TSV based 3D integration, multiple dies are thinned, aligned, and vertically bonded, thereby, enabling shorter global interconnects (and therefore reduced power consumption) and heterogeneous integration [24, 26, 29–36], as shown in Figure 2.3.

However, a typical TSV diameter is in the range of several micrometers, which is multiple orders of magnitude greater than nanoscale transistor dimensions. Furthermore, TSVs induce thermo-mechanical stress in the front-end-of-line (FEOL) layer, thereby impacting the transistor behavior [37]. Thus, bulky TSVs not only restrict the integration density but also limit the power and performance advantages of vertical integration due to significant TSV capacitance and stress [38–41].

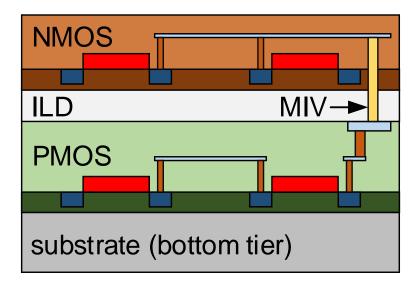

### 2.1.1.3 Monolithic 3D ICs

More recently, interest on monolithic 3D integration has grown due to encouraging developments on sequentially fabricating multiple transistor layers (particularly the thermal characteristics) [14, 42, 43]. As depicted in Figure 2.4, in monolithic vertical integration, stacked transistors are sequentially fabricated after the bottom layers have been manufactured. Communication among the tiers is achieved by monolithic inter-tier vias (MIVs). A critical challenge in the fabrication of monolithic 3D ICs is to minimize the detrimental effect of the manufacturing process of the top tier on bottom tier [44]. Thus, significant research on the fabrication side has focused on developing low thermal budget processes, typically less than 500-600°C for the upper tiers [45, 46].

Figure 2.3: Three-dimensional integration of diverse planes using TSV technology [4].

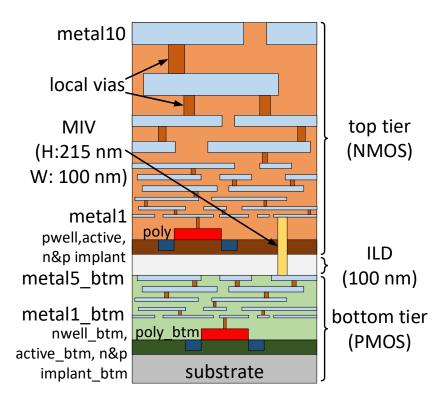

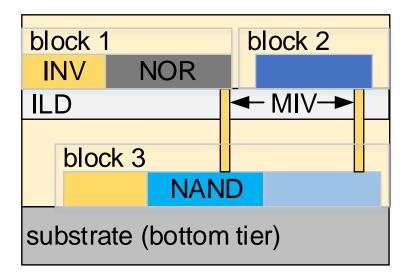

Figure 2.4: Cross-section of the transistor-level monolithic 3D technology with two tiers. The top tier hosts the nMOS transistors whereas the pMOS transistors are placed within the bottom tier.

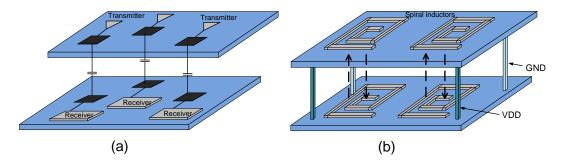

Figure 2.5: Contactless 3D integrated circuits: (a) capacitively coupled 3D integration, (b) inductively coupled 3D integration.

MIVs have comparable size to conventional on-chip metal vias since multiple tiers can be aligned with lithographic alignment precision [15]. Thus, MIV based 3D integration enables significantly higher interconnect density as compared to TSV based vertical integration.

#### 2.1.1.4 Contactless 3D ICs

Contactless 3D ICs represent another technique for communication among circuits situated on different planes. This technique relies on coupling of electrical or magnetic fields.

As shown in Figure 2.5 (a), in capacitively coupled 3D integration, on each plane there are small on-chip parallel capacitors. Transmitter and receiver modules are needed to drive the capacitors to modulate the received signals. Since transmitter and receiver electronic equipments consume significant power, capacitively coupled 3D integration is comparatively power inefficient.

In inductively coupled 3D ICs, as illustrated in Figure 2.5 (b), there is a spiral inductor located on every plane of a two-plane 3D IC. Similar to the capacitively coupled 3D integration, some specialized circuits are necessary for transmission

and receiving signals, thus, inductively coupled 3D ICs exhibit high power consumption as well. Also, the size of the inductors is typically very large [47], particularly for conventional CMOS technology where the fabrication of on-die inductor is relatively area inefficient.

### 2.1.2 Design Methodologies for Monolithic 3D ICs

Monolithic 3D integration offers multiple benefits over conventional 2D circuits. To utilize vertical integration efficiently, the technology should support a very high density of vertical interconnects with dimensions comparable to nanoscale devices, as achieved by monolithic 3D integration. There are three design styles for monolithic 3D technology: transistor-level, gate-level, and block-level, as described below.

### 2.1.2.1 Transistor-level Monolithic 3D ICs

In transistor-level monolithic 3D integration, as shown in Figure 2.6, nMOS and pMOS transistors within a circuit are separated into two different tiers. For example, the pull-down network of each gate is placed within one tier whereas the pull-up networks are placed in another tier. This approach not only achieves fine-grained 3D integration with intra-cell MIVs but also enables the individual optimization of the bottom and top tier devices [48]. Existing design automation methodologies (with modifications) can be used for this approach.

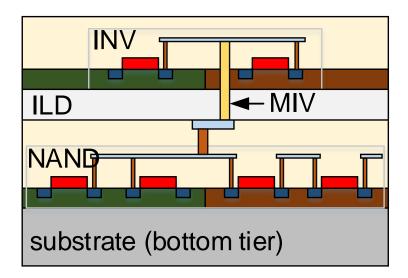

### 2.1.2.2 Gate-level Monolithic 3D ICs

In gate-level monolithic 3D integration, as shown in Figure 2.7, multiple cells

Figure 2.6: Design methodology for monolithic 3D technology: transistor-level monolithic 3D.

Figure 2.7: Design methodology for monolithic 3D technology: gate-level monolithic 3D.

Figure 2.8: Design methodology for monolithic 3D technology: block-level monolithic 3D.

within a functional block are partitioned into multiple tiers. MIVs are utilized for inter-cell communication. There is no area overhead for each cell, and a sufficiently high integration density can be achieved due to placement flexibility of the MIVs. However, novel partitioning algorithms are needed. An unbalanced partition can degrade the power and performance characteristics of gate-level monolithic 3D ICs.

### 2.1.2.3 Block-level Monolithic 3D ICs

Finally, block-level monolithic 3D integration, as shown in Figure 2.8, represents a more coarse-grain integration where the partitioning of the integrated circuit is achieved based on individual functional blocks. In this method, the benefits of monolithic 3D technology cannot be fully utilized since the high density MIVs is

not sufficiently exploited. Furthermore, proper partitioning algorithms need to be carefully applied.

The primary focus in this thesis is on transistor-level monolithic 3D integration since the benefits provided by the small dimensions of the vertical interconnects can be utilized the most. Furthermore, individual device optimizations per plane are possible in transistor-level monolithic 3D technology.

### 2.2 Existing Research on Monolithic 3D ICs

### 2.2.1 Fabrication-Level Research

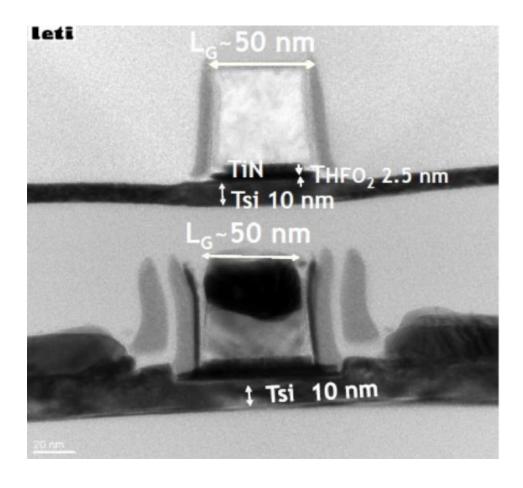

As shown in Figure 2.9, a 50nm 3D sequential structure on 10nm silicon was successfully fabricated by CEA-LETI [5]. CEA-LETI has also been collaborating with STMicroelectronics [49] and IBM [50] to develop a monolithic 3D technology with InGaAs nFET devices fabricated sequentially over SiGe pFET devices on a silicon-on-insulator (SOI) substrate.

Monolithic 3D Inc. has announced the manufacturing process of monolithic 3D wafers [51]. Transistors are built with c-Si films above the copper/low k materials to avoid alignment issues of bonding fabricated wafers. In order to not damage copper/low k layers, transistor fabrication temperature should be less than 500 - 600°C [46,52].

### 2.2.2 Design-Level Research

Hsueh et al. have demonstrated a monolithic 3D vertical cross-tier computein-memory (CIM) SRAM cell fabricated using low-cost TSV-free FinFET-based

Figure 2.9: Cross sectional image of two stacked devices fabricated through monolithic 3D integration technology [5].

3D IC technology [53]. Proposed 9T 3D CIM SRAM cell is able to compute NAND/AND, OR/NOR and XOR/XNOR operations within a single memory cycle. Proposed scheme enables the fabrication of energy and area efficient circuits for the cost-aware intelligent Internet of things (IoT) devices. As compared to the 2D version, the monolithic 3D SRAM device reduces area by 51%.

Liu and Lim have investigated the design tradeoffs in monolithic 3D ICs considering both transistor-level and gate-level monolithic integration [54]. Useful physical design guidelines and insight into the routability issue have been provided. The effects of inter-tier process variation have also been investigated. In this work, however, authors have assumed that the monolithic 3D gates and traditional 2D gates have the same power and timing characteristics. This assumption is not accurate due to different parasitic impedances within a 3D monolithic cell and the existence of MIVs.

Lee *et al.* have fixed this limitation by individually characterizing the timing and power consumption of transistor-level monolithic 3D cells [55]. The power characteristics of several 3D monolithic benchmark circuits have been investigated and compared with 2D versions at similar timing constraints. The authors, however, have adopted the cell-folding method and used the same pull-up and pull-down networks as in 2D cells. MIVs have been inserted in between these two networks. As a result, the proposed 3D cells are not optimized for the footprint. Also, in [55], the timing constraints are relatively relaxed, which may prevent to investigate the behavior of the monolithic 3D technology under tighter clock frequency constraints.

Shi *et al.* have demonstrated the power benefits of transistor-level monolithic 3D ICs through the custom design of a cell library in 14nm FinFET technology, also utilizing the cell-folding method [12]. A dedicated track is assumed for the

MIVs. A detailed cell-level *RC* extraction methodology is described. The authors, however, did not investigate the timing characteristics of the benchmark circuits. The effect of routing congestion on timing constraints and power consumption is not discussed.

# **Chapter 3**

# Mono3D: Open Source Cell Library for Monolithic 3D ICs

In this chapter, an open source standard cell library for design automation of large-scale transistor-level monolithic 3D ICs is proposed. A 256-point, highly parallelized FFT core with 1.6M cells is implemented with the proposed library. Power and timing characteristics of monolithic 3D ICs are quantified. The effect of the signal integrity and routing congestion on timing characteristics is investigated. The proposed open source cell library facilitates future research on multiple aspects of monolithic 3D technology.

The rest of this chapter is organized as follows. The details of the proposed open source cell library, characterization, and design flow are provided in Section 3.1. Power/timing and several important physical design characteristics of cells and an FFT core with monolithic 3D implementation are investigated in Section 3.2. Finally, this chapter is summarized in Section 3.3.

# 3.1 Open Source Cell Library for Monolithic 3D ICs

The characteristics of the proposed cell library are described in Section 3.1.1. The design flow to integrate the proposed library into the design process is discussed in Section 3.1.2.

# 3.1.1 Library Development

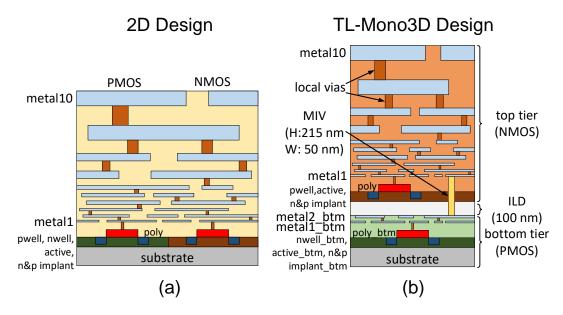

In this work, the *Mono3D*, an open source standard cell library for transistorlevel monolithic 3D technology is developed in 45 nm technology [16]. Mono3D consists of two tiers where each tier is based on the 2D 45 nm process design kit FreePDK45 from North Carolina State University (NCSU) [56]. Thus, the process and physical characteristics (transistor models and characteristics of the on-chip metal layers) are obtained from the *FreePDK45*. Similar to [12, 55], the pull-down network of a CMOS gate (nMOS transistors) is built within the top tier whereas the pull-up network (pMOS transistors) is fabricated within the bottom tier. Note that the processing temperature of the top tier is constrained to be less than 500-600°C [45] to not damage the transistors within the bottom tier. This relatively low processing temperature, however, degrades the quality of the top-tier devices. Thus, pMOS devices (that already have lower mobility) are placed within the bottom tier. As such, the proposed cell library can only be used for transistor-level monolithic 3D approach since MIVs exist within each standard cell to connect nMOS and pMOS devices. The transistor device characteristics are the same as in 2D FreePDK45. Thus, any processing temperature related degradations are not considered. However, the impact of novel devices/models and manufacturing steps for 3D monolithic integration can be captured by replacing/modifying the device

Figure 3.1: Cross-sections of the conventional 2D and transistor-level monolithic (TL-Mono) 3D technology with two tiers. The top tier hosts the nMOS transistors whereas the pMOS transistors are placed within the bottom tier.

models within the provided process design kit. System-level effects of varying device characteristics (due to, for example, the manufacturing steps of the top tiers) can, therefore, be investigated.

In the proposed *Mono3D*, two metal layers are allocated to the bottom tier (metal1\_btm and metal2\_btm), as illustrated in Figure 3.1. These metal layers are primarily for routing the intra-cell signals.

The top tier is separated from the bottom tier with an inter-layer dielectric (ILD) with a thickness of 100 nm. Inter-tier coupling is minimized at this thickness, as experimentally validated [15]. The 10 metal layers that exist in 2D *FreePDK45* are maintained the same for the top tier in *Mono3D*. The intra-cell connections that span the two tiers are achieved by MIVs. Each MIV has a width of 50 nm and a height of 215 nm [57].

| AND2X1   | INVX2    |

|----------|----------|

| AOI21X1  | INVX4    |

| BUFX2    | LATCHNEG |

| BUFX4    | MUX2X1   |

| CLKBUF1  | NAND2X1  |

| CLKBUF2  | NOR2X1   |

| CLKBUF3  | OAI21X1  |

| DFFPOSX1 | OR2X1    |

| FILL     | XNOR2X1  |

| INVX1    | XOR2X1   |

|          |          |

Table 3.1: List of standard cells in the monolithic 3D library.

Currently, 20 standard cells exist in *Mono3D*, as listed in Table 3.1. In addition to the fundamental cells, multiple clock buffers and a latch are included. Each cell is developed with a full-custom design methodology using a cell stacking technique. As opposed to [12,55] where the power (within the bottom tier) and ground (within the top tier) rails overlap, in the proposed *Mono3D*, the power rail is located at the top of the bottom tier, and ground rail is located at the bottom of the top tier. These power and ground rails at each cell row are connected to the system-level power network through power and ground rings placed during the placement and routing process.

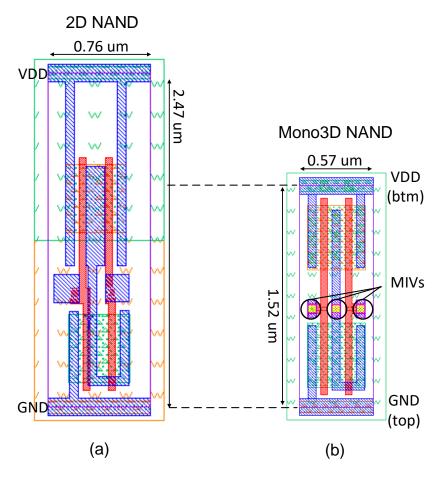

A specific track is allocated for intra-cell MIVs, which are distributed within the cell to minimize the interconnect length and reduce the cell height. Each cell within the 2D *NanGate* library has 14 routing tracks. In this thesis, monolithic 3D cell libraries are developed with 9 tracks. The number of tracks plays an essential role in chip-level routing congestion, a primary issue in monolithic 3D ICs. The cell heights in Mono3D is  $1.52 \mu m$ . This cell height is 38% shorter than the standard cell height (2.47  $\mu m$ ) in *NanGate* cell library [58].

Figure 3.2: Comparison of the layout views of a NAND gate in (a) traditional 2D technology with 14 routing tracks in each cell, (b) monolithic 3D technology with 9 routing tracks, illustrating the three MIVs used to connect the top and bottom tiers.

The layout of a NAND cell is illustrated in Figure 3.2 in both 2D and 3D monolithic technologies. Cell dimensions and the three MIVs are highlighted. Similarly, a 2D D-flip-flop cell and 3D monolithic D-flip-flop cell within *Mono3D* are compared in Figure 3.3.

In this case, the top and bottom tiers are separately depicted. Note that the width of the 3D flip-flop cell increases by approximately 7% due to MIVs and intra-cell

Figure 3.3: Comparison of the layout views of a D-flip-flop in traditional 2D and transistor-level monolithic 3D technology. The top and bottom tiers are separately depicted for the 3D technology.

routing. Also, note that particular emphasis is given to provide white space at the top tier (depending upon the number of routing tracks) to avoid pin block issue induced routing congestion.

# 3.1.2 Design Flow

The design flow adopted in this work and the modifications required for 3D monolithic technology are depicted in Figure 3.4. A new technology file (.tf) is generated for Mono3D to include all of the new layers (interconnects, via, ILD, and MIV). Based on these modifications, a new display resource file (.drf) is generated to develop full-custom layouts of the 3D cells. The design rule check (DRC), layout versus schematic (LVS) and parasitics extraction (PEX) are performed using Calibre [59]. The DRC rule file is modified to include new features for the additional

Figure 3.4: Integration of the proposed open source cell library into design flow, illustrating the required modifications.

metal layers, vias, transistors, ILD and MIV. For example, the minimum spacing between two MIVs is equal to 120 nm, producing an MIV pitch of 170 nm.

The LVS rule file is also modified for the tool to be able to identify transistors located in separate tiers independently. The extracted netlist with MIVs is analyzed to accurately obtain the interconnections between nMOS (within the top tier) and pMOS (within the bottom tier) transistors. The RC extraction rule file is modified to be able to recognize the new device tier, new metal layers, and MIVs. For metal interconnects, intrinsic plate capacitance, intrinsic fringe capacitance, and near-body (coupling) capacitance are considered between silicon and metal, and metal and metal. A single MIV is characterized by a resistance of 5.5  $\Omega$ s and a capacitance of 0.04 fF, based on [12] where device-level extraction is performed. The only parasitic component that is not considered during the extraction process is the tier-to-tier coupling capacitance. As experimentally demonstrated in [15], this component is negligible when the inter-layer dielectric is 100 nm thick.

After RC extraction, 3D cells are characterized by Encounter Library Charac-

Figure 3.5: Comparison of the automated cell library characterization process with *HSPICE* simulations: (a) clock-to-Q delay of a 3D D-flip-flop as a function of input transition time at constant load capacitance of 0.01 pF, (b) clock-to-Q delay of a 3D D-flip-flop as a function of load capacitance at constant input transition time of 120 ps.

terizer (ELC) [60] to obtain the timing and power characteristics (lookup tables) of each cell. The extracted 3D cell netlists are also simulated with HSPICE [61] to ensure the accuracy of the characterization process. For example, the clock-to-Q delay of the 3D D-flip-flop cell (as a function of input transition time and output load capacitance) obtained by HSPICE simulations is compared with ELC results (look-up tables) in Figure 3.5. As shown in this figure, ELC results sufficiently match with HSPICE simulations (with an average error of less than 4%), demonstrating the accuracy of the characterization process. More details on the area, timing, and power characteristics of the 3D cells and comparison with 2D cells are provided in Section 3.2.

The .lib file for the Mono3D generated by ELC is converted into the .db format, which is used for circuit synthesis, placement, clock tree synthesis, and routing.

Figure 3.6: Percent reduction in area achieved by each monolithic 3D cell as compared to the 2D cells. Results are provided for the 3D library, *Mono3D*.

Since all of the I/O pins of the 3D cells are located within the top tier, existing physical design tools can be used for these steps.

# 3.2 Simulation Results

# 3.2.1 Cell-Level Evaluation

## 3.2.1.1 Area

Cell-level area improvement obtained by monolithic 3D technology is shown in Figure 3.6. According to this figure, the reduction in cell area varies from -6.9%

to 59.0% in *Mono3D*, depending upon the specific cell. An average improvement of 22% is achieved for *Mono3D*. Note that a negative percent implies that the cell area increases as compared to the 2D cell. This behavior occurs for cells where the reduction in cell height causes a considerable increase in cell width. Similarly, the average area reduction is not as significant as the reduction in cell height since, on average, the cell width slightly increases due to MIVs and intra-cell routing within the reduced cell footprint.

#### 3.2.1.2 Delay and Power Consumption

MSPICE simulations are performed on the extracted 3D netlists to compare monolithic 3D technology with the conventional 2D technology at the cell level. At 1.1 V power supply, 50 ps transition time, and 27°C temperature, average delay and power consumption are analyzed, as listed in Table 3.2 for 2D and 3D technology. According to this table, Mono3D cells have, on average, 3.22% higher propagation delay and 0.46% lower power consumption as compared to the 2D standard cells. This slight increase in delay is due to denser cell layout, producing additional coupling capacitances and MIV impedances. Note that in a DFF cell, both delay (clock-to-Q delay) and power are improved as compared to 2D cells since the DFF cell has relatively longer average interconnect length where the monolithic 3D technology is helpful. Also note that the cell-level change in delay and power highly depends upon the individual cell layout, interconnects, and MIVs.

| Cells    | ]     | Delay (ps)     | Power (µW) |                |  |

|----------|-------|----------------|------------|----------------|--|

| Cells    | 2D    | 3D             | 2D         | 3D             |  |

| AND2X1   | 17.63 | 19.5 (10.6%)   | 2.82       | 3.01 (6.7%)    |  |

| AOI21X1  | 13.68 | 13.69 (0.1%)   | 3.32       | 3.34 (0.6%)    |  |

| BUFX2    | 17.89 | 17.86 (-0.2%)  | 14.04      | 13.92 (-0.9%)  |  |

| BUFX4    | 15.82 | 15.29 (-3.4%)  | 29.00      | 28.98 (-0.1%)  |  |

| CLKBUF1  | 27.01 | 27.32 (1.2%)   | 64.07      | 62.52 (-2.4%)  |  |

| CLKBUF2  | 39.57 | 40.17 (1.5%)   | 93.25      | 90.88 (-2.5%)  |  |

| CLKBUF3  | 51.73 | 53.04 (2.5%)   | 121.4      | 119.0 (-2.0%)  |  |

| DFFPOSX1 | 41.69 | 34.72 (-16.7%) | 26.75      | 27.18 (1.6%)   |  |

| INVX1    | 6.73  | 6.42 (-4.6%)   | 4.69       | 4.68 (-0.2%)   |  |

| INVX2    | 6.54  | 6.32 (-3.4%)   | 9.31       | 9.24 (-0.8%)   |  |

| INVX4    | 6.44  | 6.29 (-2.3%)   | 18.01      | 18.16 (0.8%)   |  |