Rhapsody: Methodology and Algorithms for

Automated Architecture Generation for Analog and

Mixed-Signal Systems

Research Team

Alex

Doboli, Hua Tang and

Hui

Zhang

Research Goal and Objectives

Our goal was to develop methodologies and techniques for automated

generation of high-level analog system architectures. This task is know

as high-level architecture generation(HAG).

HAG bridges the gap between an abstract description of a system, e.g.

in MATLAB or VHDL-AMS, and the circuit level implementation of the system.

Inputs to HAG are abstract, unsized netlist of blocks, as well as performance/design

constraints for the final implementation. Typical performance constraints

refer to silicon area, offset voltages, bandwidth, poles and zeros, settling

time, signal-to-noise ratio (SNR), dynamic range (DR), and so on. The output

of HAG is the sized architectural netlist, in which each block has its

performance/design requirements identified. After HAG, circuit synthesis

is performed in a subsequent step to create the transistor level design

for each block in the system architecture.

The proposed HAG methodology includes three main activities:

Block parameter exploration/optimization:

This step finds the block parameter values that optimize the imposed system

performance. This module also evaluates the quality of each architectural

solution. Block parameter exploration relies on exploration algorithms

driven by performance model estimation.

Floorplanning and global routing: This

activity designs the silicon floorplan of a system and routes the inputs,

outputs and power lines of the analog blocks in an architecture. Floorplanning

and global routing are very important for extracting and estimating layout

parasitic, i.e. crosstalk and RLC interconnect parasitic.

System performance evaluation: This

task involves fast yet accurate performance estimation. Evaluation addresses

linear and non-linear parameters in time and frequency domains.

Importance

Without proper HAG tools, it will be impossible to address the increasing

productivity gap and benefit from upcoming technological advancements.

Every year, the number of transistors per chip rises by 58%, whereas the

design productivity increases by only 21%. In addition, modern SoC are

characterized by complex functionalities, diverse performance requirements,

and heterogeneous components (e.g., digital, analog and RF). For example,

MPEG-4 and H.263 encoders, network processors, and software radio are typical

mixed-signal SoC. Digital hardware and software are optimized for cost,

speed, and power consumption. In contrast, analog and RF circuits must

meet specific constraints, e.g. linearity, bandwidth, dynamic range, and

image rejection. Hence, HAG approaches are needed for mixed-domain specification,

trade-off exploration, and integration.

Related Publications

Hua Tang, Hui Zhang, A. Doboli, "Refinement based

Synthesis of Continuous-Time Analog Filters Through Successive Domain Pruning,

Plateau Search and Adaptive Sampling", under review, IEEE Transactions

on CAD, May 2004.

Doboli, R. Vemuri, "Behavioral Modeling for High-Level

Synthesis of Analog and Mixed-Signal Systems from VHDL-AMS", IEEE Transactions

on CAD of Integrated Circuits and Systems, Vol. 22, No. 11, 2003.

A. Doboli, R. Vemuri, "Exploration-Based High-Level

Synthesis of Linear Analog Systems Operating at Low/Medium Frequencies",

IEEE Transactions on CAD of Integrated Circuits and Systems, Vol. 22, No.

11 2003.

H. Tang, H. Zhang, A. Doboli, "Towards High-Level

Synthesis of Analog and Mixed-Signal Systems from VHDL-AMS Specifications

- A Case Study for a Sigma-Delta Analog-Digital Converter", in C. Grimm,

editor, "Languages for System Specification and Verification", Kluwer,

2004.

H. Zhang, A. Doboli, S. Doboli, "Fast Time-Domain

Simulation Through Combined Symbolic Analysis and Piecewise Linear Modeling",

Proc. of the IEEE Behavioral Modeling and Simulation Workshop (BMAS'04),

San Jose, 2004.

H. Zhang, A. Doboli, "Fast Time Domain Symbolic Simulation

for Synthesis of S-D Analog-Digital Converters", Proc. of the International

Symposium on Circuits and Systems, Vancouver, 2004.

H. Tang, H. Zhang, A. Doboli, "Towards High-Level

Synthesis of Analog and Mixed-Signal Systems from VHDL-AMS Specifications

- A Case Study for a Sigma-Delta Analog-Digital Converter", Forum on Specification

and Design Languages (FDL'03), Frankfurt, 2003.

S. Doboli, A. Doboli, "Piecewise-Linear Modeling

of Analog Circuits using Trained Feed-Forward Neural Networks and Adaptive

Clustering of Hidden Neurons", Proc. of the 2003 International Joint Conference

on Neural Networks (IJCNN), Portland, 2003.

H. Tang, H. Zhang, A. Doboli, "Synthesis of Continuous-Time

Filters and Analog to Digital Converters by Integrated Constraint Transformation,

Floorplanning and Routing", Proc. of the Great Lakes Symposium on VLSI

(GLSVLSI), Washington DC, 2003.

H. Tang, H. Zhang, A. Doboli, "Layout-Aware Analog

System Synthesis Based on Symbolic Layout Description and Combined Block

Parameter Exploration, Placement and Routing", Proc. of the Annual Symposium

on VLSI (ISVLSI), Tampa, 2003.

S. Doboli, G. Gothoskar, A. Doboli, "Extraction of

Piecewise-Linear Analog Circuit Models from Trained Neural Networks using

Hidden Neuron Clustering", Proc. of the Design, Automation and Test in

Europe Conference (DATE), Munich, 2003.

S. Doboli, G. Gothoskar, A. Doboli, "Piecewise-Linear

Modeling of Analog Circuits Based on Model Extraction from Trained Neural

Networks", Proc. of the Behavioral Modeling and Simulation Workshop (BMAS),

Santa Rosa, 2002.

H. Tang, A. Doboli, "Layout-Aware Synthesis for Analog

Systems Based on Combined Block Sizing, Floorplanning and Global Routing",

poster, 2002 ASIC/SOC Conference, September 25-27 2002, Rochester, NY.

H. Tang, A. Doboli, "Employing Layout Templates for

Synthesis of Analog Systems", Proc. of the 45th Midwest Symposium on Circuits

and Systems, Tulsa, OK, August 6-8 2002.

Overview of the high-level architecture generation

methodology

The developed HAG methodology and algorithms include two synthesis components

and one simulation module. The two synthesis components implement a two

phase HAG process. Phase 1 corresponds to layout independent synthesis,

and is continued by Phase 2, layout aware HAG. Phase 1 tackles a

simplified synthesis problem (without layout parasitic), but uses minimal

designer knowledge as input. The outputs of Phase 1 are inputs for Phase

2. Phase 2 considers layout parasitic but starts from the feasible design

points found in Phase 1. The third module is fast yet accurate simulation

methodology. We mainly focused on fast simulation of Sigma-Delta analog

to digital converters (ADC).

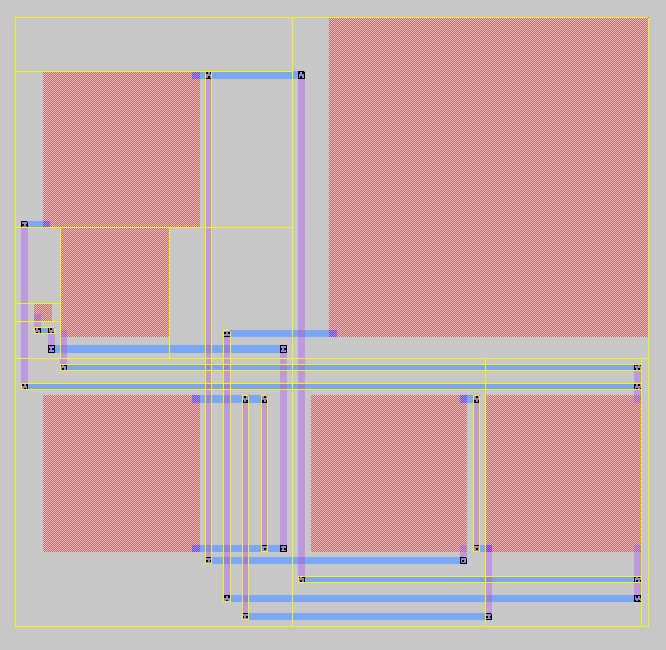

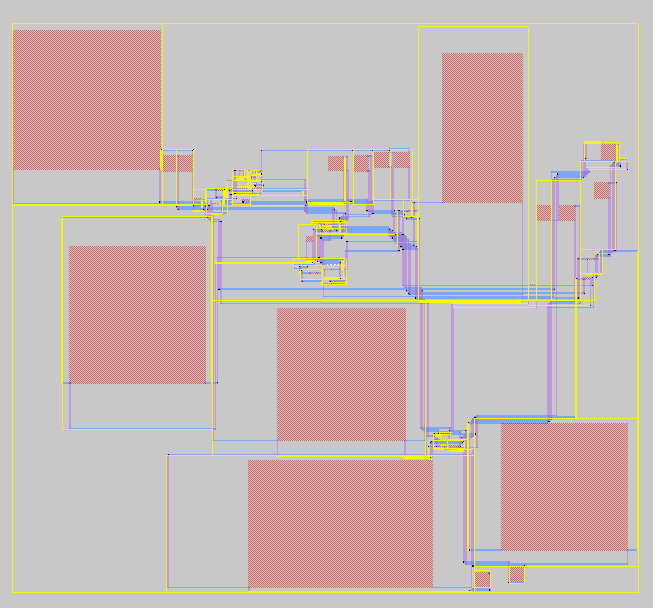

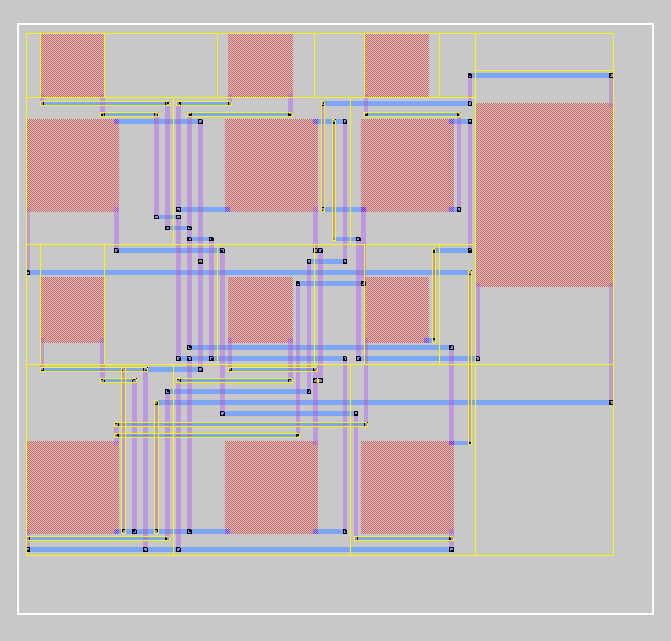

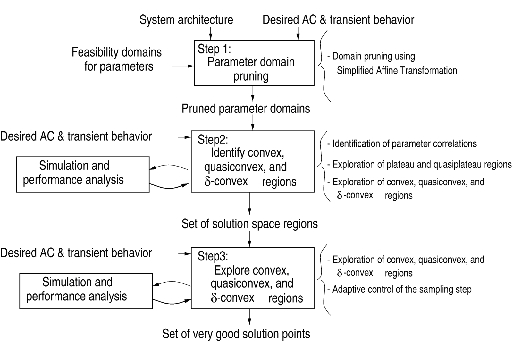

Figure 1 presents the layout independent high-level

architecture generation and system synthesis phase. Inputs to

the flow are system architectures and performance requirements in AC and

transient domains. Architectures are netlists of active circuits, such

as op amps and GmC, and passive elements, like resistors and capacitors.

Synthesis output is a set of performance satisfying system architectures

having all their resistors and capacitors sized, and with circuit performance

constraints identified, like op amp/GmC gains, poles, I/O impedances, and

so on. For the identified circuit constraints, op amp/GmC transistors can

be sized using state-of-the-art circuit synthesis tools.

Figure 1: Phase 1 - Layout independent high-level architecture

generation}

The flow consists of three successive steps:

Parameter domain pruning. The first

step eliminates plateau regions, which largely violate performance constraints,

thus determine large cost function values.

Finding convex, quasiconvex and d-convex

regions. After parameter domain pruning, the remaining regions

are subject to a filtering process that identifies convex, quasiconvex,

and d-convex regions by eliminating remaining

plateau or quasiplateau areas. The algorithm for this step is called plateau

search, and it includes distinct exploration strategies for different space

region types. Simulated annealing was used for convex, quasiconvex and

d-convex

regions. For plateau and quasiplateau, the developed strategy conducts

a uniform sampling of the space, as the goal was to isolate other promising

regions, and not improve upon current points (like for convex regions).

Exploring convex, quasiconvex and d-convex

regions. This step isolates good quality local optima situated

in the regions found at the end of the second step. This step uses an adaptive

sampling step, so that rift regions are also properly analyzed.

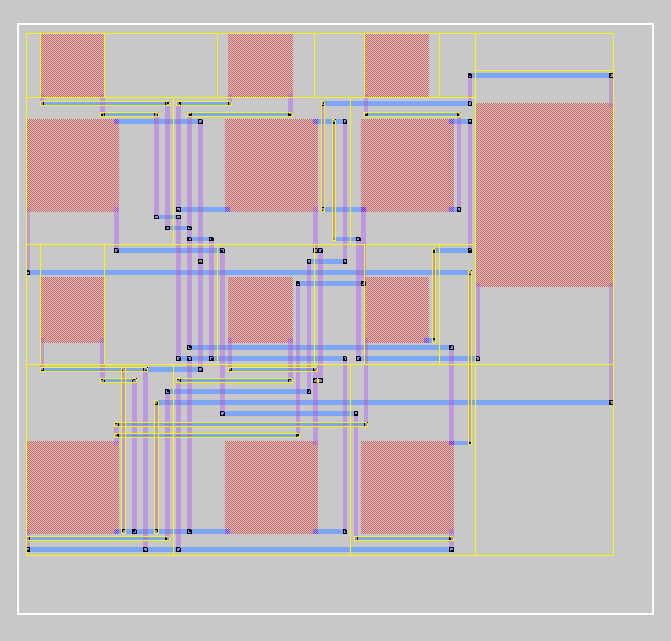

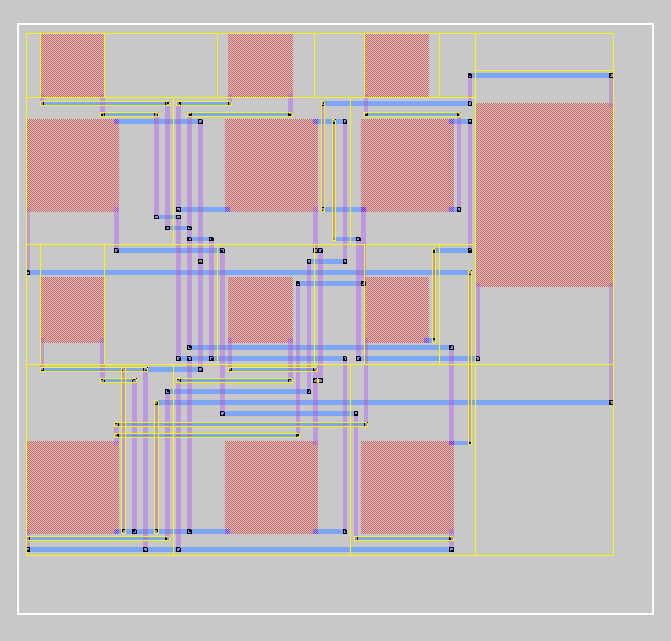

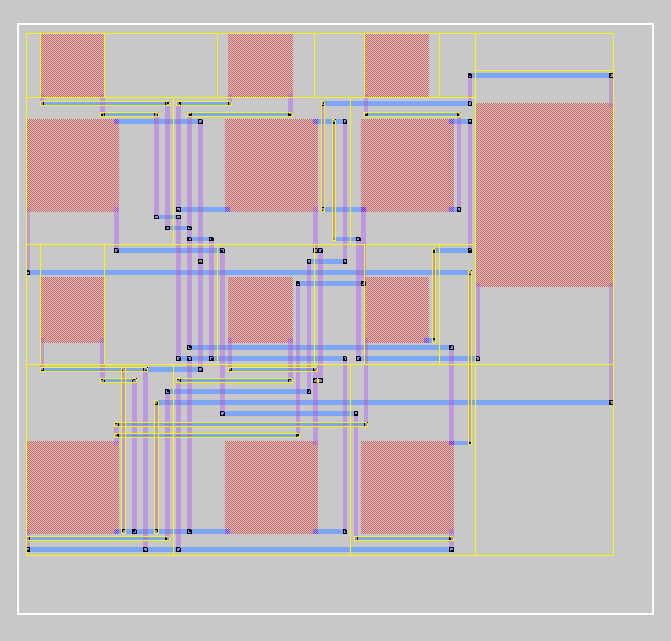

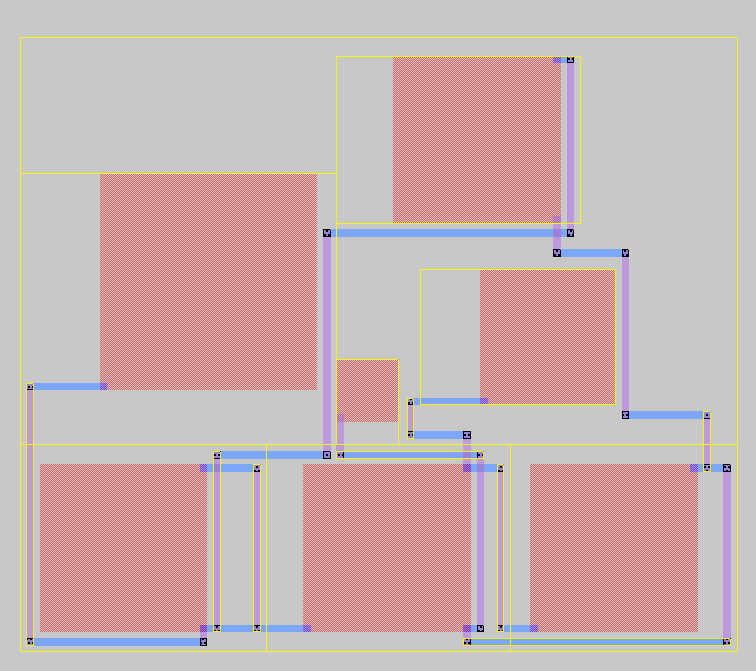

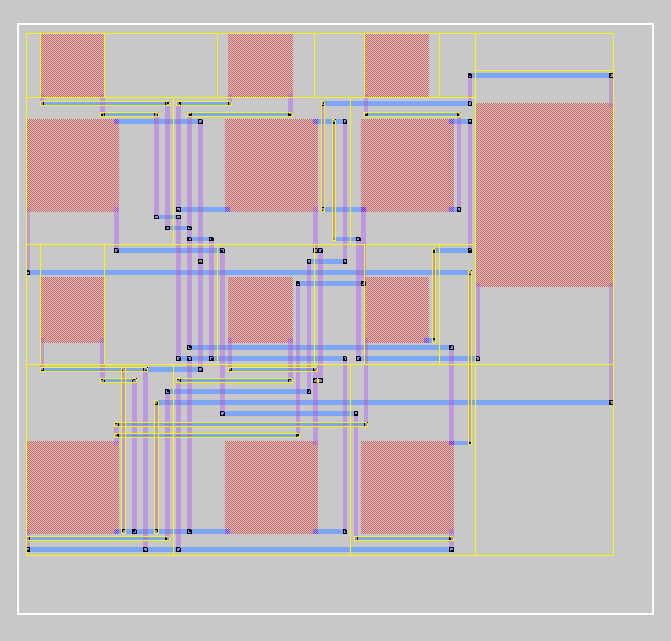

The second phase is layout-aware HAG.

It combines block parameter exploration, block placement and global signal

routing. The method combines (1) block placement and (2) global routing

with (3) block parameter exploration. Inputs to the methodology are system

architectures with parameters sized at Phase 1 (layout independent HAG).

AC and transient performances are evaluated for each circuit using SPICE

simulations. There are two key elements for this technique: (1) an original

layout representation to uniformly express block parameter exploration,

placement, signal routing under precise modeling of layout parasitic, and

(2) specific algorithms that use the layout representation for synthesis.

Layout is described symbolically using Layout Constraint Graphs (LCG).

LCGs present mathematical constraints for block dimensions, block positions,

wire routings and symmetries. The proposed synthesis algorithms use LCGs

for block parameter search, block moving and swapping, block overlapping

resolution and wire routing.

The third component represents a new approach to fast

time-domain simulation of analog systems that contain nonlinear

parameters. Without trading accuracy, the proposed technique achieves speed-ups

of more than 10nx as compared to numerical (Spectre) simulation by generating

compiled-code for simulation. Code generation relies on calculating symbolic

expressions for the output voltages and currents, and the state variables

of a system. Code optimization identifies and eliminates all loop invariants,

and propagates constant sub-expressions present in the simulation loop.

Code generation uses detailed structural macromodels for the building blocks

(OTA, opamp, and comparator), including non-idealities, like finite gain,

poles and zeros, CMRR, phase margin, fall and rise time, and so on. Nonlinear

parameters are described using piecewise linear (PWL) models. Our research

focused primarily on fast simulation of Sigma-Delta ADC.

Additional Information

Following are additional insight into Rhapsody synthesis environment:

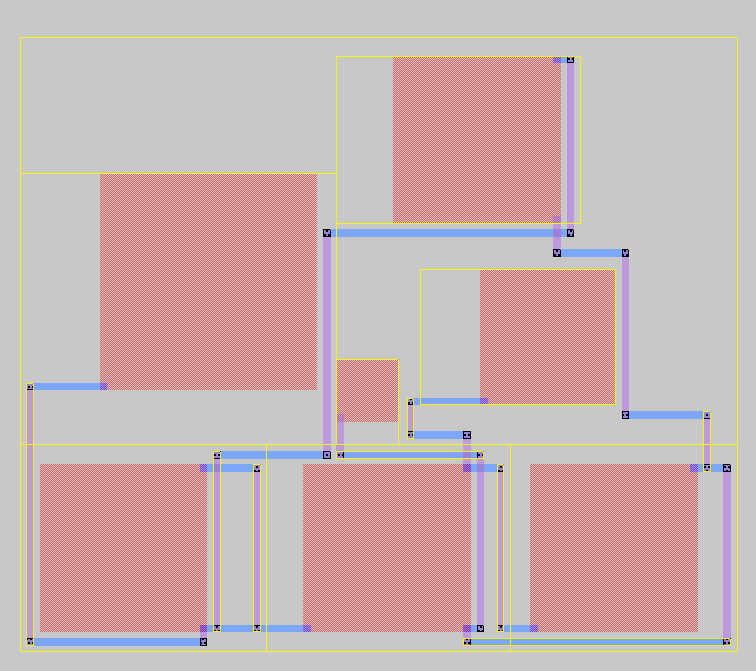

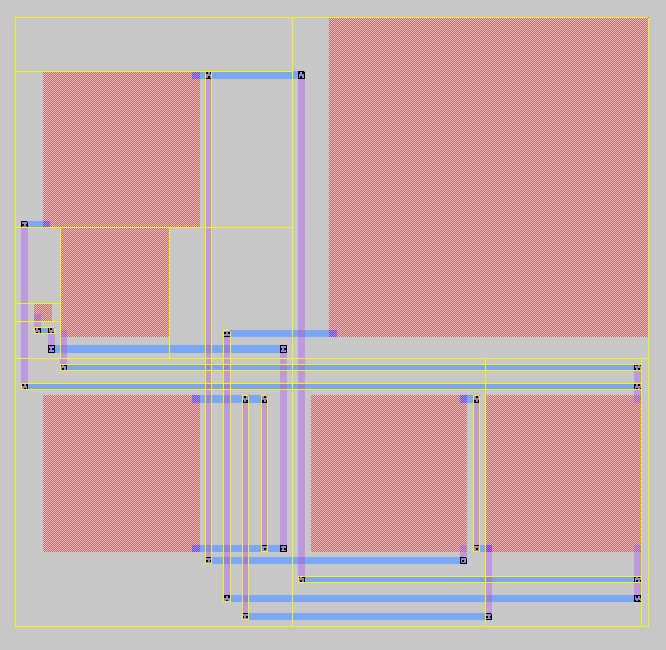

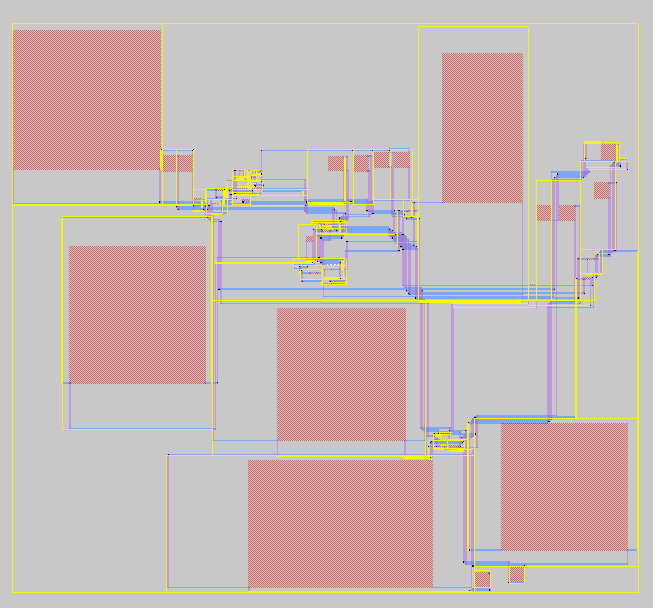

Rhapsody synthesis tool - a

layout-aware, user-friendly analog system synthesis environment. Inputs

are structural descriptions of an architecture, and outputs are architectural

blocks with their parameters identified and MAGIC files for the system

floorplan and global routing. The tool was realized in C/C++, and runs

under UNIX OS. A Graphical User Interface (GUI) was also included. Snapshots

from the tool: overview, new project

definition, running, ... running,

result 1 and result 2.

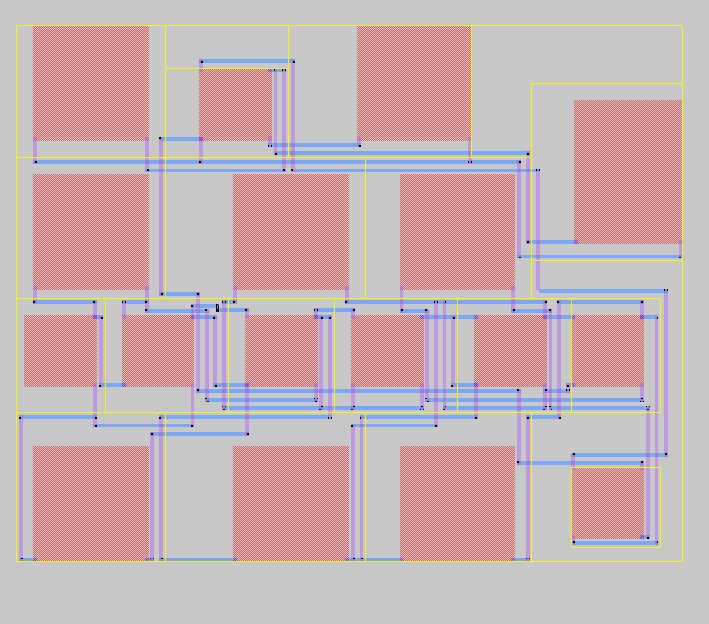

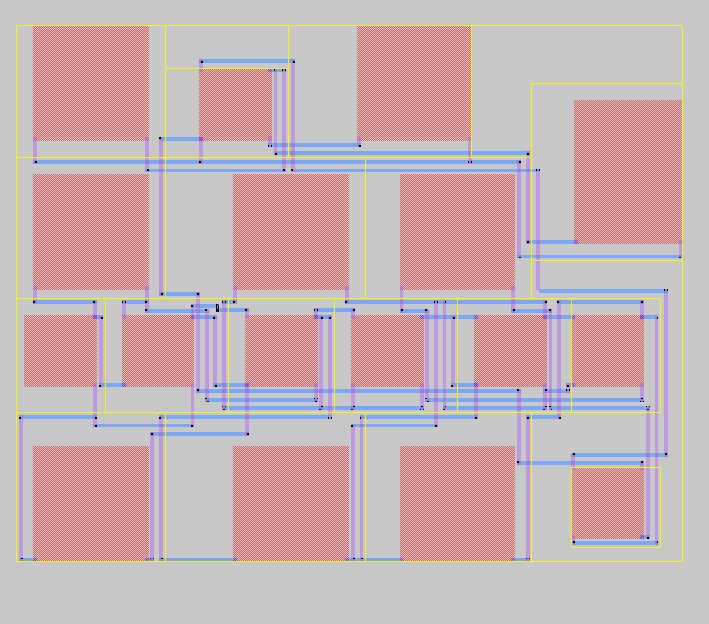

Synthesis results for several high frequency

filters (1MHz-100MHz range) and Sigma-Delta ADC (2nd, 3rd, and 4th order).

Other synthesis results:

3rd order elliptic filter (100MHz): 3rd order Sigma-Delta

ADC:

3rd order elliptic filter (12MHz):

4th order Sigma-Delta ADC:

6th order filter: